- 您現(xiàn)在的位置:買賣IC網 > PDF目錄383982 > UPD703201 (NEC Corp.) 32-BIT SINGLE-CHIP MICROCONTROLLERS PDF資料下載

參數資料

| 型號: | UPD703201 |

| 廠商: | NEC Corp. |

| 英文描述: | 32-BIT SINGLE-CHIP MICROCONTROLLERS |

| 中文描述: | 32位單晶片微控制器 |

| 文件頁數: | 60/98頁 |

| 文件大小: | 797K |

| 代理商: | UPD703201 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁當前第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁

Preliminary Product Information U15436EJ1V0PM

60

μ

PD703201, 703201Y, 703204, 703204Y, 70F3201, 70F3201Y, 70F3204, 70F3204Y

(4/6)

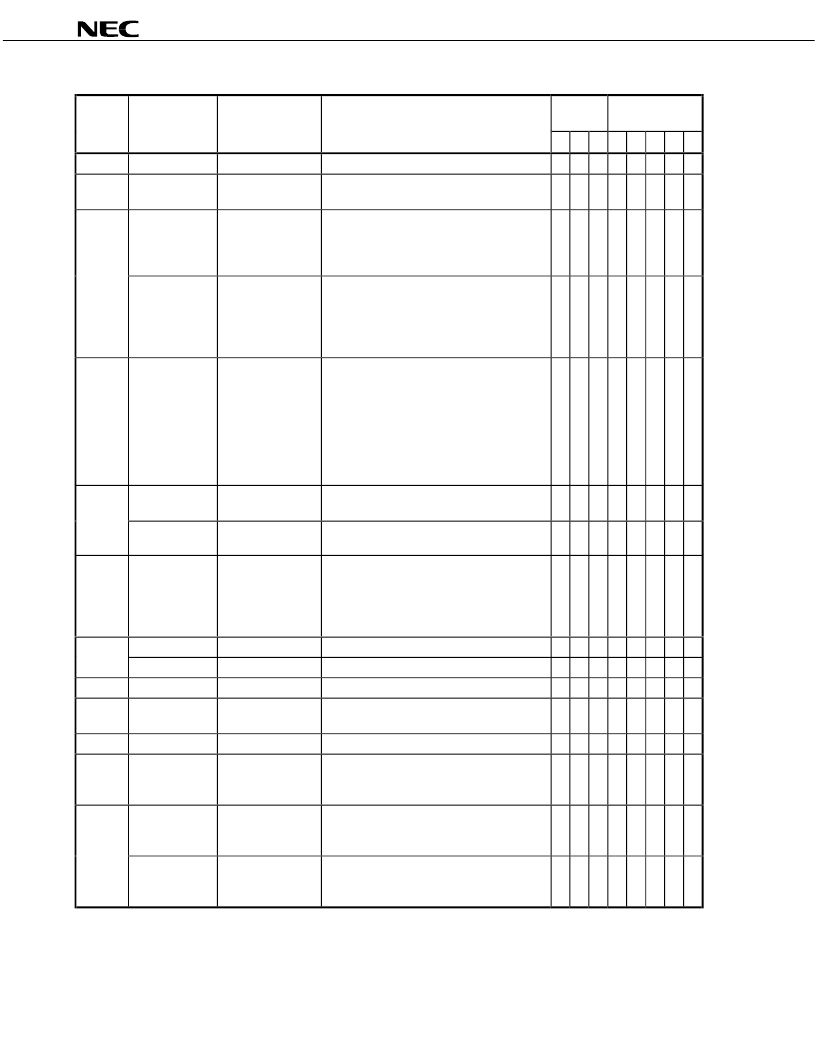

Execution

Clock

Flags

Mnemonic

Operand

Opcode

Operation

i

r

l

CY OV

S

Z SAT

OR

reg1,reg2

rrrrr001000RRRRR

GR[reg2]

←

GR[reg2]OR GR[reg1]

1

1

1

0

×

×

ORI

imm16,reg1,reg2

rrrrr110100RRRRR

i i i i i i i i i i i i i i i i

GR[reg2]

←

GR[reg1]OR zero-extend(imm16)

1

1

1

0

×

×

list12,imm5

00000 1111 0iiiiiL

LLLLLLLLLLL00001

Store-memory(sp–4,GR[reg in list12],Word)

sp

←

sp–4

repeat 1 step above until all regs in list12 is stored

sp

←

sp-zero-extend(imm5)

n+1

Note 4

n+1

Note 4

n+1

Note 4

PREPARE

list12,imm5,

sp/imm

Note 14

00000 1111 0iiiiiL

LLLLLLLLLLLff011

imm16/imm32

Note 15

Store-memory(sp–4,GR[reg in list12],Word)

sp

←

sp–4

repeat 1 step above until all regs in list12 is stored

sp

←

sp-zero-extend(imm5)

ep

←

sp/imm

n+2

Note 4

Note 16

n+2

Note 4

Note 16

n+2

Note 4

Note 16

RETI

0000011111100000

0000000101000000

if PSW.EP=1

then PC

PSW

←

EIPSW

else if PSW.NP=1

then

←

EIPC

PC

PSW

←

FEPSW

PC

←

EIPC

PSW

←

EIPSW

←

FEPC

else

3

3

3

R

R

R

R

R

reg1,reg2

rrrrr111111RRRRR

0000000010100000

GR[reg2]

←

GR[reg2]arithmetically shift right

by GR[reg1]

1

1

1

×

0

×

×

SAR

imm5,reg2

r r r r r 0 1 0 1 0 1 i i i i i

GR[reg2]

←

GR[reg2]arithmetically shift right

by zero-extend (imm5)

1

1

1

×

0

×

×

SASF

cccc,reg2

rrrrr1111110cccc

0000001000000000

if conditions are satisfied

then GR[reg2]

←

(GR[reg2]Logically shift left by 1)

OR 00000001H

else GR[reg2]

←

(GR[reg2]Logically shift left by 1)

OR 00000000H

1

1

1

reg1,reg2

rrrrr000110RRRRR

GR[reg2]

←

saturated(GR[reg2]+GR[reg1])

1

1

1

×

×

×

×

×

SATADD

imm5,reg2

r r r r r 0 1 0 0 0 1 i i i i i

GR[reg2]

←

saturated(GR[reg2]+sign-extend(imm5)

1

1

1

×

×

×

×

×

SATSUB

reg1,reg2

rrrrr000101RRRRR

GR[reg2]

←

saturated(GR[reg2]–GR[reg1])

1

1

1

×

×

×

×

×

SATSUBI

imm16,reg1,reg2

rrrrr110011RRRRR

i i i i i i i i i i i i i i i i

GR[reg2]

←

saturated(GR[reg1]–sign-extend(imm16)

1

1

1

×

×

×

×

×

SATSUBR

reg1,reg2

rrrrr000100RRRRR

GR[reg2]

←

saturated(GR[reg1]–GR[reg2])

1

1

1

×

×

×

×

×

SETF

cccc,reg2

rrrrr1111110cccc

0000000000000000

If conditions are satisfied

then GR[reg2]

←

00000001H

else GR[reg2]

←

00000000H

1

1

1

bit#3,disp16[reg1]

00bbb111110RRRRR

dddddddddddddddd

adr

←

GR[reg1]+sign-extend(disp16)

Z flag

←

Not (Load-memory-bit(adr,bit#3))

Store-memory-bit(adr,bit#3,1)

3

Note 3

3

Note 3

3

Note 3

×

SET1

reg2,[reg1]

rrrrr111111RRRRR

0000000011100000

adr

←

GR[reg1]

Z flag

←

Not(Load-memory-bit(adr,reg2))

Store-memory-bit(adr,reg2,1)

3

Note 3

3

Note 3

3

Note 3

×

相關PDF資料 |

PDF描述 |

|---|---|

| UPD703204 | 32-BIT SINGLE-CHIP MICROCONTROLLERS |

| UPD70F30025AGC-25 | LJT 24C 12#16 12#12 PIN PLUG |

| UPD70F3004AGC-33 | 32-bit RISC Microcontrollers |

| UPD70F3004AGC-25 | 32-bit RISC Microcontrollers |

| UPD7030025AGC-25 | LJT 24C 12#16 12#12 PIN PLUG |

相關代理商/技術參數 |

參數描述 |

|---|---|

| UPD703201GC-XXX-8EU | 制造商:NEC 制造商全稱:NEC 功能描述:32-BIT SINGLE-CHIP MICROCONTROLLERS |

| UPD703201Y | 制造商:NEC 制造商全稱:NEC 功能描述:32-BIT SINGLE-CHIP MICROCONTROLLERS |

| UPD703201YGC-XXX-8EU | 制造商:NEC 制造商全稱:NEC 功能描述:32-BIT SINGLE-CHIP MICROCONTROLLERS |

| UPD703204 | 制造商:NEC 制造商全稱:NEC 功能描述:32-BIT SINGLE-CHIP MICROCONTROLLERS |

| UPD703204F1-XXX-EA6 | 制造商:NEC 制造商全稱:NEC 功能描述:32-BIT SINGLE-CHIP MICROCONTROLLERS |

發(fā)布緊急采購,3分鐘左右您將得到回復。