- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383960 > TMP470R1B768PGE (Texas Instruments, Inc.) 16/32-Bit RISC Flash Microcontroller PDF資料下載

參數(shù)資料

| 型號: | TMP470R1B768PGE |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | 16/32-Bit RISC Flash Microcontroller |

| 中文描述: | 16/32位RISC閃存微控制器 |

| 文件頁數(shù): | 38/50頁 |

| 文件大?。?/td> | 393K |

| 代理商: | TMP470R1B768PGE |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁當(dāng)前第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁

www.ti.com

! "$&

! "$&

$

%#$

$#

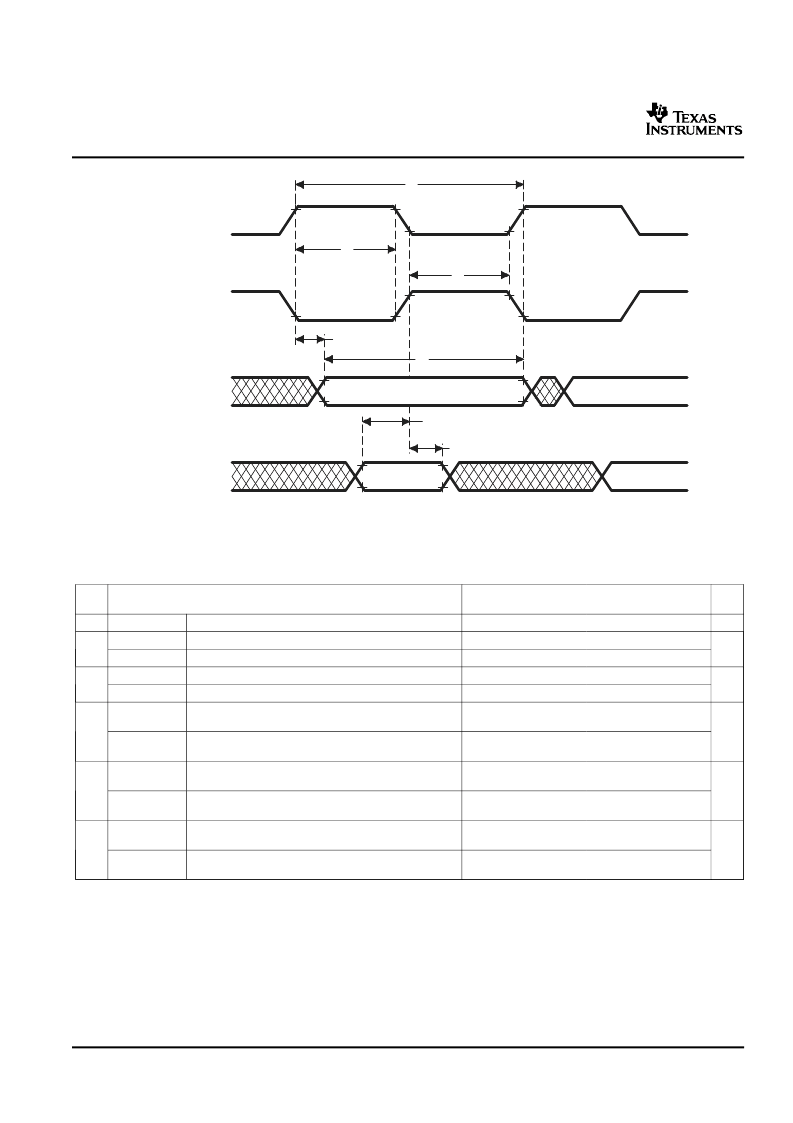

SPIn Slave Mode External Timing Parameters

(CLOCK PHASE = 1, SPInCLK = input, SPInSIMO = input, and SPInSOMI = output)

(1)(2)(3)(4)

(see

Figure 15

)

TMS470R1B768

16/32-Bit RISC Flash Microcontroller

SPNS108A–AUGUST 2005–REVISED AUGUST 2006

Figure 14. SPIn Slave Mode External Timing (CLOCK PHASE = 0)

NO.

MIN

MAX

UNI

T

ns

1

t

c(SPC)S

t

w(SPCH)S

t

w(SPCL)S

t

w(SPCL)S

t

w(SPCH)S

Cycle time, SPInCLK

(5)

Pulse duration, SPInCLK high (clock polarity = 0)

Pulse duration, SPInCLK low (clock polarity = 1)

Pulse duration, SPInCLK low (clock polarity = 0)

Pulse duration, SPInCLK high (clock polarity = 1)

Valid time, SPInCLK high after SPInSOMI data valid

(clock polarity = 0)

Valid time, SPInCLK low after SPInSOMI data valid

(clock polarity = 1)

Valid time, SPInSOMI data valid after SPInCLK high

(clock polarity = 0)

Valid time, SPInSOMI data valid after SPInCLK low

(clock polarity = 1)

Setup time, SPInSIMO before SPInCLK high

(clock polarity = 0)

Setup time, SPInSIMO before SPInCLK low

(clock polarity = 1)

100

256t

c(ICLK)

0.5t

c(SPC)S

– 0.25t

c(ICLK)

0.5t

c(SPC)S

– 0.25t

c(ICLK)

0.5t

c(SPC)S

– 0.25t

c(ICLK)

0.5t

c(SPC)S

– 0.25t

c(ICLK)

0.5t

c(SPC)S

+ 0.25t

c(ICLK)

0.5t

c(SPC)S

+ 0.25t

c(ICLK)

0.5t

c(SPC)S

+ 0.25t

c(ICLK)

0.5t

c(SPC)S

+ 0.25t

c(ICLK)

2

(6)

ns

3

(7)

ns

t

v(SOMI-SPCH)S

0.5t

c(SPC)S

– 6 – t

r

4

(7)

ns

t

v(SOMI-SPCL)S

0.5t

c(SPC)S

– 6 – t

f

t

v(SPCH-SOMI)S

0.5t

c(SPC)S

– 6 – t

r

5

(7)

ns

t

v(SPCL-SOMI)S

0.5t

c(SPC)S

– 6 – t

f

t

su(SIMO-SPCH)S

6

6

(6)

ns

t

su(SIMO-SPCL)S

6

(1)

(2)

(3)

(4)

(5)

The MASTER bit (SPInCTRL2.3) is cleared and the CLOCK PHASE bit (SPInCTRL2.0) is set.

If the SPI is in slave mode, the following must be true: t

≥

(PS + 1) t

, where PS = prescale value set in SPInCTL1[12:5].

For rise and fall timings, see the "Switching Characteristics for Output Timings versus Load Capacitance" table.

t

= interface clock cycle time = 1/f

When the SPIn is in slave mode, the following must be true:

For PS values from 1 to 255: t

c(SPC)S

≥

(PS +1)t

c(ICLK)

≥

100 ns, where PS is the prescale value set in the SPInCTL1[12:5] register bits.

For PS values of 0: t

= 2t

≥

100 ns.

The active edge of the SPInCLK signal referenced is controlled by the CLOCK POLARITY bit (SPInCTRL2.1).

The active edge of the SPInCLK signal referenced is controlled by the CLOCK POLARITY bit (SPInCTRL2.1).

(6)

(7)

38

Submit Documentation Feedback

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TMP47C020 | Transient Voltage Suppressor Diodes |

| TMP47C020G | Transient Voltage Suppressor Diodes |

| TMP47C050 | Transient Voltage Suppressor Diodes |

| TMP47C050E | Transient Voltage Suppressor Diodes |

| TMP47C050G | Transient Voltage Suppressor Diodes |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TMP470R1F369APGEQ | 制造商:Texas Instruments 功能描述: |

| TMP470R1VF338PZQ | 制造商:Texas Instruments 功能描述:- Rail/Tube |

| TMP470R1VF478GJZQ | 制造商:Texas Instruments 功能描述: |

| TMP4720/7440P/N | 制造商:未知廠家 制造商全稱:未知廠家 功能描述: |

| TMP4720F | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:4-Bit Microcontroller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。