- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383959 > TMC2193KJC (FAIRCHILD SEMICONDUCTOR CORP) 10 Bit Encoder PDF資料下載

參數(shù)資料

| 型號: | TMC2193KJC |

| 廠商: | FAIRCHILD SEMICONDUCTOR CORP |

| 元件分類: | 消費(fèi)家電 |

| 英文描述: | 10 Bit Encoder |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| 封裝: | MQFP-100 |

| 文件頁數(shù): | 26/72頁 |

| 文件大?。?/td> | 448K |

| 代理商: | TMC2193KJC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁當(dāng)前第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁

TMC2193

PRODUCT SPECIFICATION

26

REV. 1.0 3/26/03

Enabling the pedestal on line 25 enables it for the remainder

of field 1, to line 262. Likewise, enabling the pedestal on line

288 enables it for the remainder of field 2.

Pedestal Height

There are two control registers that set the pedestal height,

PEDHGT1, and PEDHGT2. PEDHGT1 determines the

height of the pedestal for the luminance channel on the com-

posite path and PDEHGT2 determines the height of the ped-

estal for the luminance channel on the component path. This

allows for independent pedestal control of the composite and

component paths. In both cases the range of the pedestal

height is from -22.1 to 21.74 IRE in .345 IRE increments.

Sync and Blank Insertion

The control register NBMD selects the sync and blank levels

for the component path, so that the correct ratio of sync to

blank and blank to 100% white for both a 5:2 and 7:3 stan-

dards are meet. If NBMD is LOW the component blank level

is a D/A code of 256 (314 mV), this is added to the lumi-

nance data for YPbPr or all three components for RGB out-

puts. The component sync level is a D/A code of 12 (14 mV)

which is added to the luminance data for YPbPr or to the

Green component for RGB outputs. If NBMD is HIGH the

component blank level is a D/A code of 240 (295 mV), this

is added to the luminance data for YPbPr or all three compo-

nents for RGB outputs. The component sync level is a D/A

code of 8 (9 mV) which is added to the luminance data for

YPbPr or to the Green component for RGB outputs. The

selection of which components have sync and blank codes

added to them is controlled by the OUTMODE control regis-

ter. Which can select from YPbPr, RGB with sync on green

or RGB with external sync.

For the composite path the blank and sync D/A codes are

determined by the FORMAT control register. For NTSC and

PAL-M formats the blank D/A code is 240 (295 mV) and the

sync D/A code is 8 (9 mV). For all other PAL formats the

blank D/A code is 256 (314 mV) and the sync D/A code is

12 (14 mV).

In all cases the sync edges are sloped to insure the proper rise

and fall times in all video standards.

Closed Caption Insertion

Control Registers for this section

The TMC2193 includes a flexible closed-caption processor.

It may be programmed to insert a closed caption signal on

any line within a range of 16 lines on ODD and/or EVEN

fields. Closed Caption insertion overrides all other configura-

tions of the encoder: if it is specified on an active video line,

it takes precedence over the video data and removes NTSC

setup if setup has been programmed for the active video

lines. Closed Caption is only available when the TMC2193

is in a 13.5 MHz pixel rate.

Closed caption is turned on by setting CCON HIGH. When-

ever the encoder begins producing a line specified by

CCFLD and CCLINE, it will insert a closed caption line in

its place. If CCRTS is HIGH, the data contained in CCDx

will be sent. IF CCRTS is LOW, Null bytes (hex 00 with

ODD parity) will be sent.

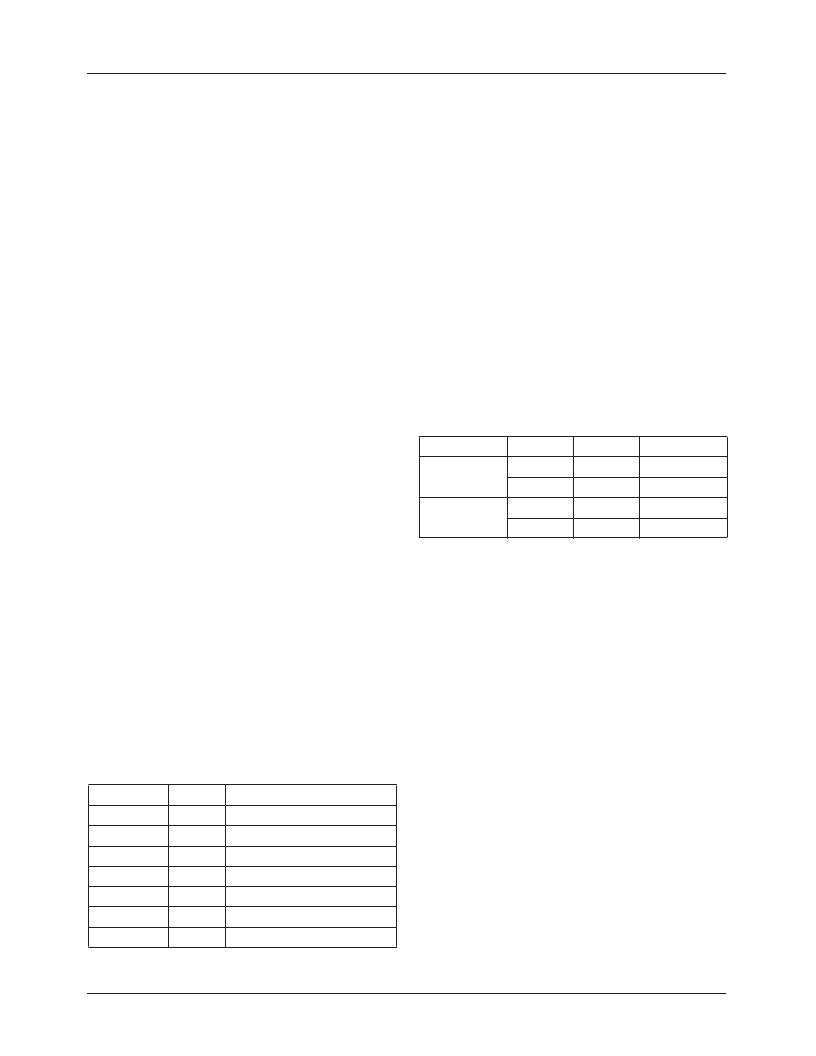

Line Selection

The line to contain CC data is selected by a combination of

the CCFLD bit and the CCLINE bits. CCLINE is added to

the offset shown in Table 16 to specify the line.

Parity Generation

Standard Closed-Caption signals employ ODD parity, which

may be automatically generated by setting CCPAR HIGH.

Alternatively, parity may be generated externally as part of

the bytes to be transmitted, and, with CCPAR LOW, the

entire 16 bits loaded into the CCDx registers will be sent

unchanged.

Operating Sequence

A typical operational sequence for closed-caption insertion

on line xx is:

Read Register 1E and check that bit 7 is LOW, indicat-

ing that the CCDx registers are ready to accept data.

If ready, write two bytes of CC data into registers 1C

and 1D.

Write into register 1E the proper combination of

CCFLD and CCLINE. CCPAR may be written as

desired. Set CCRTS HIGH.

The CC data is transmitted during the specified line.

As soon as CCDx s transferred into the CC processor (and

CCRTS goes LOW), new data may be loaded into registers

1C and 1D. This allows the user to transmit CC data on sev-

eral consecutive lines by loading data for line n+1 while data

is being sent on line n.

Address

0x1C

0x1D

0x1E

0x1E

0x1E

0x1E

0x1E

Bit(s)

7-6

1-0

7

6

5

4

3

–

0

Name

CCD1

CCD2

CCON

CCRTS

CCPAR

CCFLD

CCLINE

Table 16. Closed Caption Line Selection

Standard

525

Offset

12

274

16

328

Field

ODD

EVEN

ODD

EVEN

Lines

12-27

274-289

16-31

328-343

625

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TMC2193 | 10 Bit Encoder |

| TMC22051AKHC | Circular Connector; No. of Contacts:11; Series:MS27484; Body Material:Aluminum; Connecting Termination:Crimp; Connector Shell Size:18; Circular Contact Gender:Pin; Circular Shell Style:Straight Plug; Insert Arrangement:18-11 RoHS Compliant: No |

| TMC22X5YA | Multistandard Digital Video Decoder Three-Line Adaptive Comb Decoder Family, 8 & 10 bit |

| TMC22052AKHC | Multistandard Digital Video Decoder Three-Line Adaptive Comb Decoder Family, 8 & 10 bit |

| TMC22053AKHC | Multistandard Digital Video Decoder Three-Line Adaptive Comb Decoder Family, 8 & 10 bit |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TMC22 WAF | 制造商:Fairchild Semiconductor Corporation 功能描述: |

| TMC22051 WAF | 制造商:Fairchild Semiconductor Corporation 功能描述: |

| TMC22051AKHC | 功能描述:多媒體雜項 RoHS:否 制造商:Texas Instruments 類型: 通道數(shù)量: 轉(zhuǎn)換速率:540 Mbps 分辨率: 封裝 / 箱體:SOIC-16 封裝:Tube |

| TMC22052AKHC | 制造商:FAIRCHILD 制造商全稱:Fairchild Semiconductor 功能描述:Multistandard Digital Video Decoder Three-Line Adaptive Comb Decoder Family, 8 & 10 bit |

| TMC22053AKHC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。