- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383959 > TMC2072 (Fairchild Semiconductor Corporation) Genlocking Video Digitizer PDF資料下載

參數(shù)資料

| 型號: | TMC2072 |

| 廠商: | Fairchild Semiconductor Corporation |

| 英文描述: | Genlocking Video Digitizer |

| 中文描述: | 同步鎖相視頻數(shù)字化儀 |

| 文件頁數(shù): | 6/21頁 |

| 文件大小: | 160K |

| 代理商: | TMC2072 |

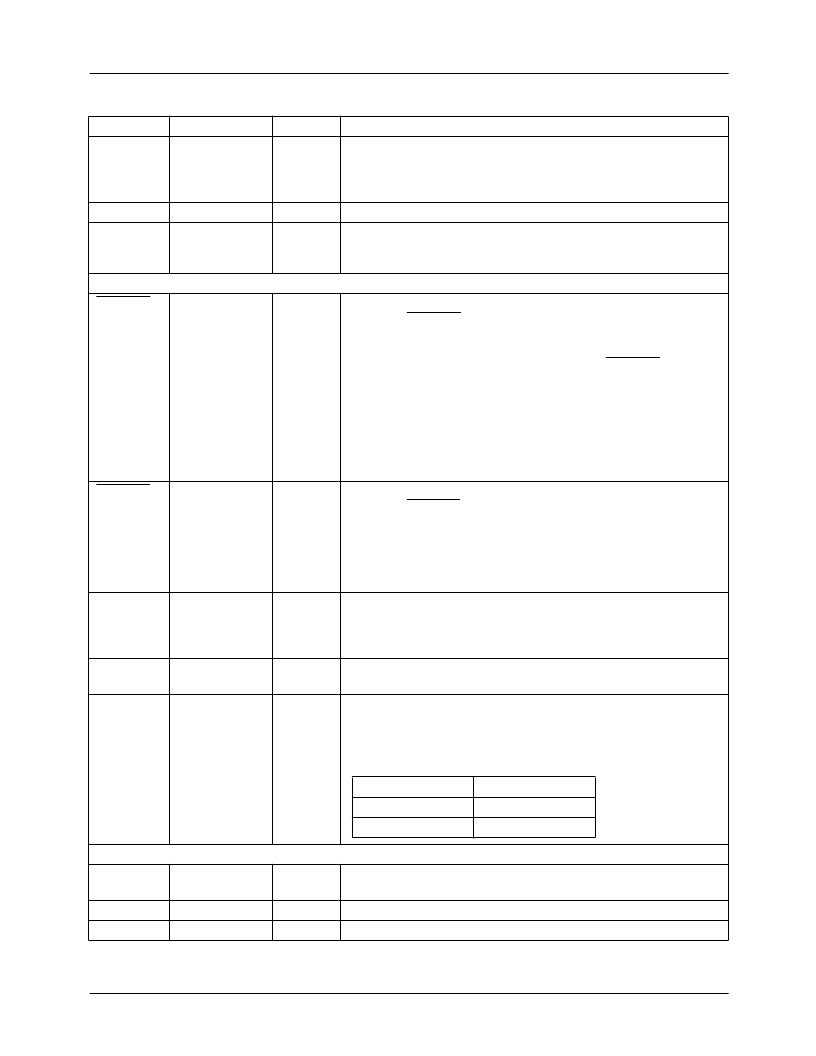

TMC2072

PRODUCT SPECIFICATION

6

REV. 1.0.4 6/19/01

LDV

40

CMOS

Pixel clock output.

Delayed pixel clock output. LDV runs at 1/2 the

rate of PXCK and its rising edge is useful for transferring CVBS

digital video from the TMC2072 to the TMC22x9x Digital Video

Encoders.

External PXCK input.

Input for external PXCK clock source.

PXCK source select.

Select input for internal or external PXCK.

When HIGH, the internally generated line-locked PXCK is selected.

When LOW, the external PXCK source is enabled.

EXT PXCK

PXCK SEL

94

86

CMOS

CMOS

Digital Video

GHSYNC

32

CMOS

Horizontal sync output.

When the TMC2072 is locked to incoming

video, the GHSYNC pin provides a negative-going pulse after the

falling edge of each horizontal sync pulse. When the device is

locked to a stable video signal, there is a fixed number of PXCK

clock cycles between adjacent falling edges of GHSYNC. If no video

signal is present and LEADLAG is less than 4A(hex), the TMC2072

will output normal, evenly-spaced horizontal pulses. If no video

signal is present and LEADLAG exceeds 88(hex), the TMC2072 will

omit every eighth Hsync pulse. As LEADLAG is increased from 49h

to 89h, seven out of every eight Hsyncs will be unaffected, but the

eighth will shrink by one clock cycle per LSB step, until it disappears

entirely at 89h.

Vertical sync output.

When the TMC2072 is locked to incoming

video, the GVSYNC pin provides a negative-going edge after the

start of the first vertical sync pulse of a vertical blanking interval. If

no video signal is present on the selected input pin, GVSYNC will

remain continuously at logic high, until a signal is selected and lock

is reestablished. A system designer requiring a free-running vertical

sync may wish to provide this with an external pixel counter.

Composite output bus.

8-bit composite video data are output on

this bus at 1/2 the PXCK rate. During horizontal sync, field ID,

subcarrier frequency, and subcarrier phase are available on this

bus.

Odd/even (

“

top/bottom

”

) field flag. LOW denotes the first field of a

video frame; HIGH, the second.

Bruch blanking flag. In PAL, LOW denotes a frame with burst

blanked on line 310, whereas HIGH denotes burst detected on line

310. FID[1] is valid only in PAL and only when FID[0] is high and

should be interpreted as follows:

GVSYNC

33

CMOS

CVBS

7-0

30-28, 25-21

CMOS

FID[0]

35

CMOS

FID[1]

36

CMOS

μ

P l/O

SA[2:0]

3-1

R-bus chip address, 3 LSBs.

Full 7-bit address = {1, 0, 0, 0, SA[2],

SA[1], SA[0]}

R-bus bidirectional data line.

R-bus clock line (input/slave only)

SDA

SCL

4

5

R-bus

R-bus

Pin De

fi

nitions

(continued)

Pin Name

Pin Number

Pin Type

Function

FID[1:0]

01

11

PAL Field Number

II or VI

IV or VIII

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TMC2192KHC | 10 Bit Encoder |

| TMC2193KJC | 10 Bit Encoder |

| TMC2193 | 10 Bit Encoder |

| TMC22051AKHC | Circular Connector; No. of Contacts:11; Series:MS27484; Body Material:Aluminum; Connecting Termination:Crimp; Connector Shell Size:18; Circular Contact Gender:Pin; Circular Shell Style:Straight Plug; Insert Arrangement:18-11 RoHS Compliant: No |

| TMC22X5YA | Multistandard Digital Video Decoder Three-Line Adaptive Comb Decoder Family, 8 & 10 bit |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TMC2072_07 | 制造商:SMSC 制造商全稱:SMSC 功能描述:Peripheral Mode CircLink⑩ Controller |

| TMC2072KHC | 功能描述:視頻 IC Video Digitizer Genlocking RoHS:否 制造商:Fairchild Semiconductor 工作電源電壓:5 V 電源電流:80 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-28 封裝:Reel |

| TMC2072-MD | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC Peripheral Mode CircLink Cntlr RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| TMC2072-MT | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC Peripheral Mode CircLink Cntlr RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| TMC2074 | 制造商:SMSC 制造商全稱:SMSC 功能描述:Dual Mode CircLink⑩ Controller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。