- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383959 > TMC2072 (Fairchild Semiconductor Corporation) Genlocking Video Digitizer PDF資料下載

參數(shù)資料

| 型號: | TMC2072 |

| 廠商: | Fairchild Semiconductor Corporation |

| 英文描述: | Genlocking Video Digitizer |

| 中文描述: | 同步鎖相視頻數(shù)字化儀 |

| 文件頁數(shù): | 11/21頁 |

| 文件大?。?/td> | 160K |

| 代理商: | TMC2072 |

PRODUCT SPECIFICATION

TMC2072

REV. 1.0.4 6/19/01

11

0

ENAGC

Re-Enable Automatic Gain Control

. HIGH (self-resetting one-shot): Initiates a

new, self-terminating one-frame AGC sequence, independent of sync lock status.

LOW (power-on default and self-reset): AGC is enabled for one frame when video

sync is initially acquired, and each time sync is lost and reacquired. [TMC22071A

bit 25].

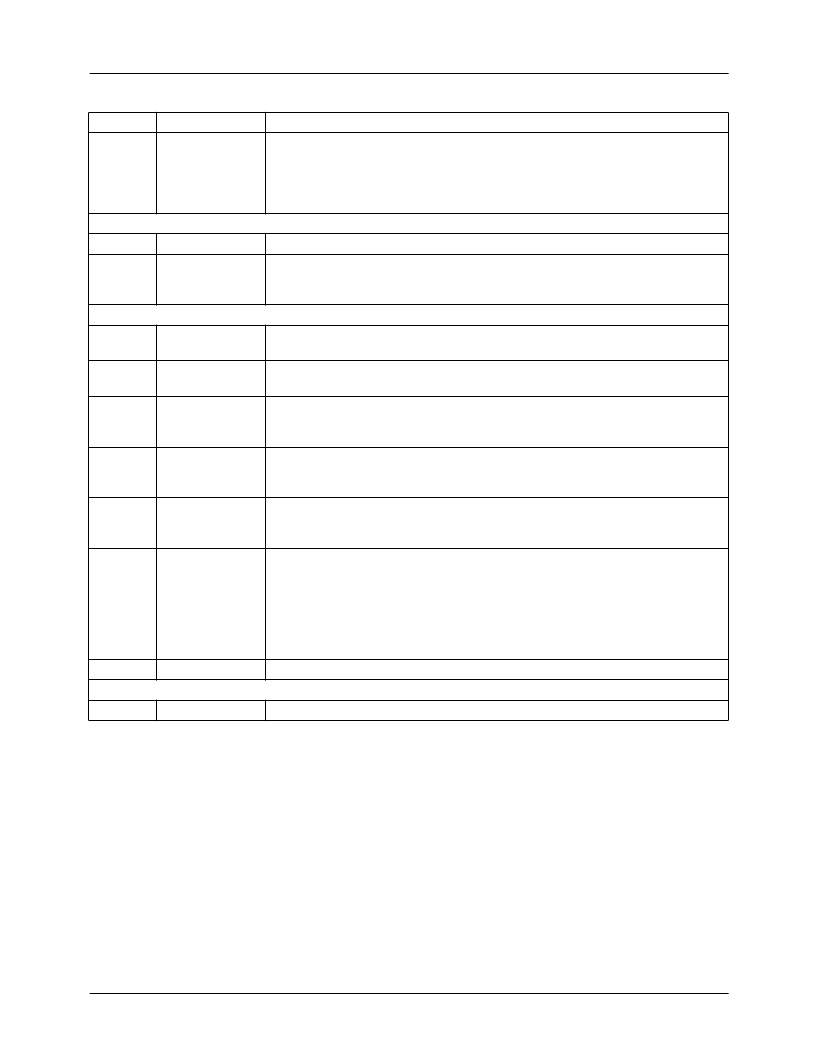

Reg 0D Sync Tip Set

7:4

3:0

Reserved

Programmable Sync Tip Value

. Power-on default = 0. Recommended setting =

3. When the chip has achieved stable lock, this will be the average value output

over CVBS during sync tips and equalization pulses. [TMC22071A bit 43:40.]

ST[3:0]

Reg 0E

7

FLIPPX

LOW (power-on default): Phase of PXCK output matches that of the TMC22071A.

HIGH: Phase of PXCK output is inverted, relative to that of the TMC22071A.

LOW (power-on default): Phase of LDV output matches that of the TMC22071A.

HIGH: Phase of LDV output is inverted, relative to that of the TMC22071A.

LOW (power-on default): PXCK output timing matches that of TMC22071A.

HIGH: PXCK output is delayed approximately 5-10ns, to simplify interface timing

in some systems.

LOW (power-on default): LDV output timing matches that of TMC22071A. HIGH:

LDV output is delayed approximately 5-10ns, to simplify interface timing in some

systems.

LOW (power-on default): Digital outputs CVBS0-7, FID(2:0) and GV/GHSYNC

are tristated, to avoid bus contentions elsewhere on the system. HIGH: These

pins are enabled, for normal operation.

LOW (power-on default): If the Hloop loses lock (Hlock\ goes high), the CVBS

port will output the default subcarrier frequency and cumulative phase keyed to

each GHSYNC falling edge, and the raw output of the A/D converter at all other

times. In this case, since the incoming video and internal state machine are

asynchronous, GRS data may appear anywhere along each digitized video line.

HIGH: If the Hloop loses lock, the CVBS data port will yield only the default

subcarrier phase and frequency data, and zero at all other times.

Reserved

, reset low (power-on default)

6

FLIPLDV

5

XDLY

4

VDLY

3

ENVHCVBS

2

FORCEZERO

1:0

Reg 0F

7:0

Reserved

, reset low (power-on default)

Details

(continued)

Bit

Name

Function

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TMC2192KHC | 10 Bit Encoder |

| TMC2193KJC | 10 Bit Encoder |

| TMC2193 | 10 Bit Encoder |

| TMC22051AKHC | Circular Connector; No. of Contacts:11; Series:MS27484; Body Material:Aluminum; Connecting Termination:Crimp; Connector Shell Size:18; Circular Contact Gender:Pin; Circular Shell Style:Straight Plug; Insert Arrangement:18-11 RoHS Compliant: No |

| TMC22X5YA | Multistandard Digital Video Decoder Three-Line Adaptive Comb Decoder Family, 8 & 10 bit |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TMC2072_07 | 制造商:SMSC 制造商全稱:SMSC 功能描述:Peripheral Mode CircLink⑩ Controller |

| TMC2072KHC | 功能描述:視頻 IC Video Digitizer Genlocking RoHS:否 制造商:Fairchild Semiconductor 工作電源電壓:5 V 電源電流:80 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-28 封裝:Reel |

| TMC2072-MD | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC Peripheral Mode CircLink Cntlr RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| TMC2072-MT | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC Peripheral Mode CircLink Cntlr RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| TMC2074 | 制造商:SMSC 制造商全稱:SMSC 功能描述:Dual Mode CircLink⑩ Controller |

發(fā)布緊急采購,3分鐘左右您將得到回復。