- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359289 > TEA5764HN (NXP SEMICONDUCTORS) FM radio + RDS PDF資料下載

參數(shù)資料

| 型號: | TEA5764HN |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 接收器 |

| 英文描述: | FM radio + RDS |

| 中文描述: | FM, AUDIO SINGLE CHIP RECEIVER, PQCC40 |

| 封裝: | 6 X 6 MM, 0.85 MM HEIGHT, PLASTIC, MO-220, SOT-618-1, HVQFN-40 |

| 文件頁數(shù): | 25/64頁 |

| 文件大小: | 287K |

| 代理商: | TEA5764HN |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁當前第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁

TEA5764HN_2

Koninklijke Philips Electronics N.V. 2005. All rights reserved.

Product data sheet

Rev. 02 — 9 August 2005

25 of 64

Philips Semiconductors

TEA5764HN

FM radio + RDS

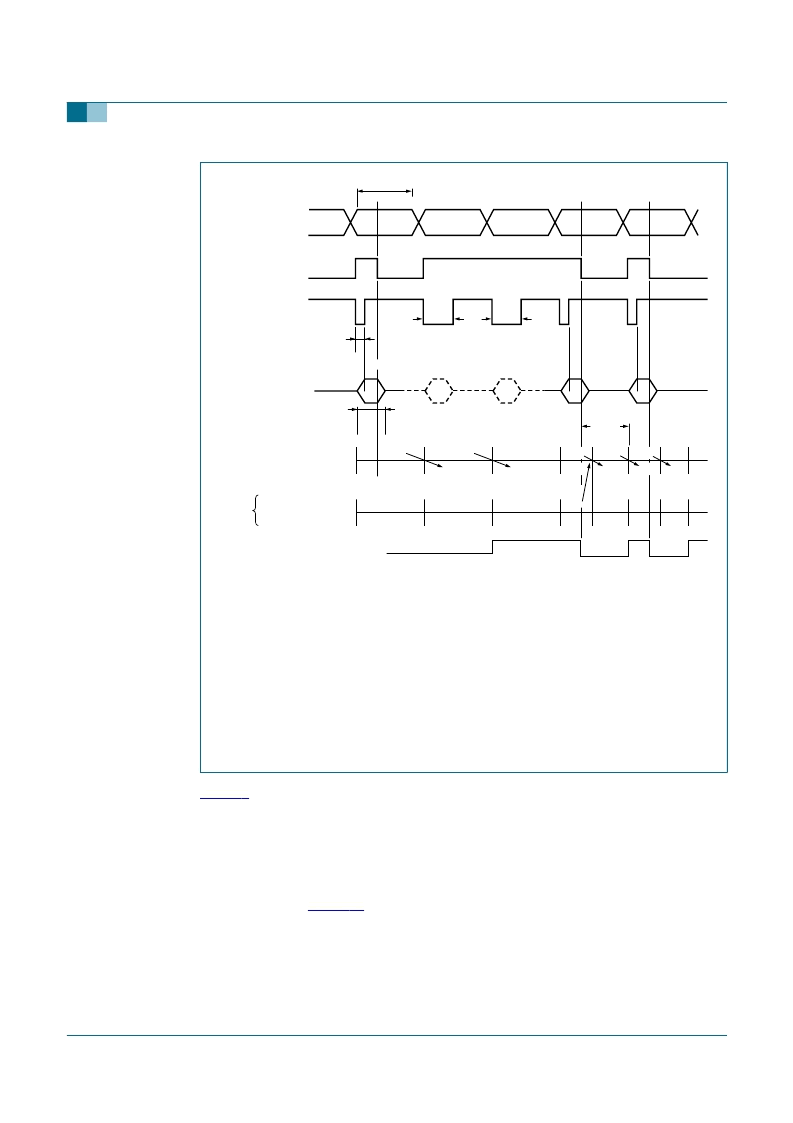

Figure 9

assumes that block synchronization has been achieved and that no other

interrupt flags are being set.

10.2 DAV-B processing mode / fast PI search mode

This mode is used, for example, when the receiver has been re-tuned to a new station,

and a fast search of the PI code, always contained in the A or C’ block, is required. The

diagram shown in

Figure 10

, assumes that the RDS decoder is unsynchronized initially

and is performing a synchronization search.

During synchronization search the decoder does not set the DAVFLG until a valid A or C’

block is detected. If a valid B block is detected immediately, then the decoder is now

synchronized and bit SYNC is set to logic 1. In fact, if any 2 good blocks in a valid order

are detected, the RDS decoder will synchronize and give an interrupt.

Bit DOVF set when 2 new blocks received in BL and BP registers

(1) If there is no read cycle, B

1

is placed in the BP register and the new block C

1

is now in the BL

register. Bit DOVF is set to indicate two blocks available.

(2) Data is not transferred to BL register at the end of the read period/clear DOVF, D

1

is missed.

(3) In order not to lose D

1

a read must be performed before D

1

enters decoder buffer, thus read

finishes within 21 ms after DOVF set to logic 1.

(4) DOVF is cleared when the BL register is read. To be of use, DOVF has to be read before BL

and BP registers.

(5) To prevent DOVF being set again, an extra read of BL must be performed before A2 has been

decoded.

Fig 9.

DAV-A timing diagram, DAV-A/B: normal

001aab471

A

1

21.9 ms

DAVFLG

DAVFLG set

on falling edge

DAVN = 0, cleared

on read BL register

INTX

B

1

read BL

end read intmsk

read intflg

+

RDS on INTX

t

INT_RD

t

READ

BL register

BP register

A

1

x

t

INT_RD

<

≈

10 ms

read BL

read BL

C

1

D

1

A

2

B

2

C

2

B

1

A

1

(1)

(3)

(2)

A

2

D

1

(4)

(2)

(1)

(5)

C

1

B

1

D

1

C

1

B

2

A

2

being decoded

in the decoder buffer

B

1

A

1

data overflow bit

C

1

B

1

D

1

C

1

A

2

D

1

C

1

B

1

A

2

D

1

A

2

A

2

B

2

A

2

B

2

A

1

decoder

registers:

9.98 ms

9.98 ms

>

2 ms

相關PDF資料 |

PDF描述 |

|---|---|

| TEA5764UK | FM radio + RDS |

| TEF6700HL | Car radio tuner front-end for digital IF |

| TEF6701HL | Car radio tuner front-end for digital IF |

| TEMUX-84 | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| TFDT4000 | Integrated Transceiver |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| TEA5764HN2GE | 制造商:STMicroelectronics 功能描述: |

| TEA5764UK | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:FM radio + RDS |

| TEA5764UK/N2,027 | 功能描述:調(diào)諧器 FM RADIO WITH RDS RoHS:否 制造商:NXP Semiconductors 功能: 噪聲系數(shù): 工作電源電壓: 最小工作溫度: 最大工作溫度: |

| TEA5764UK-G | 功能描述:調(diào)諧器 FM RADIO WITH RDS RoHS:否 制造商:NXP Semiconductors 功能: 噪聲系數(shù): 工作電源電壓: 最小工作溫度: 最大工作溫度: |

| TEA5766UK/N1,023 | 功能描述:調(diào)節(jié)器/解調(diào)器 FM RADIO + RDS RoHS:否 制造商:Texas Instruments 封裝 / 箱體:PVQFN-N24 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復。