- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385814 > SAA7392 (NXP Semiconductors N.V.) Channel encoder/decoder CDR60(通道編碼器/譯碼器) PDF資料下載

參數(shù)資料

| 型號: | SAA7392 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | Channel encoder/decoder CDR60(通道編碼器/譯碼器) |

| 中文描述: | 信道編碼器/解碼器CDR60(通道編碼器/譯碼器) |

| 文件頁數(shù): | 15/76頁 |

| 文件大小: | 246K |

| 代理商: | SAA7392 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁當(dāng)前第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁

2000 Mar 21

15

Philips Semiconductors

Preliminary specification

Channel encoder/decoder CDR60

SAA7392

7.2.6

I

NTERRUPT

E

NABLE

R

EGISTER

2 (I

NT

E

N

2)

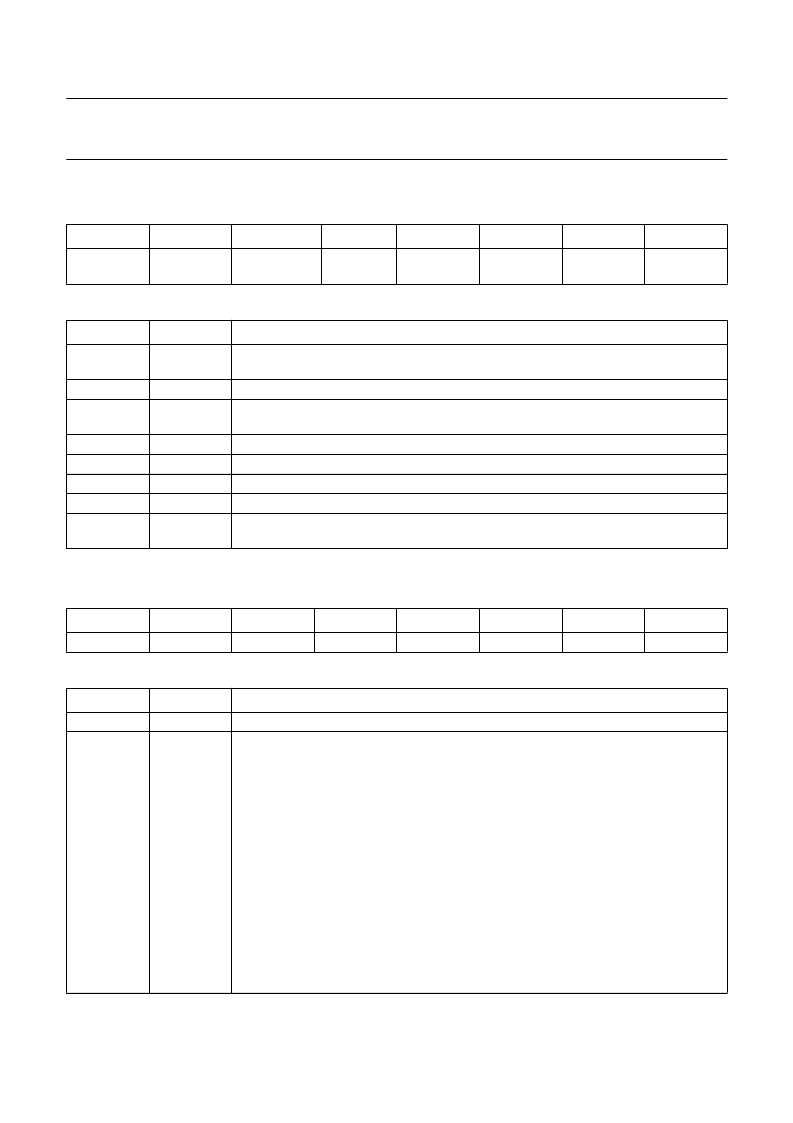

Table 13

Interrupt Enable Register 2 (address 21H) - WRITE

Table 14

Description of IntEn2 bits

7.2.7

S

OFT

R

ESET

R

EGISTER

(S

OFT

R

ESET

)

Table 15

Soft Reset Register (address 1BH) - WRITE

Table 16

Description of SoftReset bits

7

6

5

4

3

2

1

0

BankSwitch

En

SyncErrorEn

DataNotValid

En

QSyncEn

ATIPSyncEn

LaserOnEn

LaserOffEn

XErrorLarge

En

BIT

SYMBOL

DESCRIPTION

7

BankSwitch

En

SyncErrorEn If SyncErrorEn = 1, then SyncError interrupt is enabled.

DataNotVali

dEn

QSyncEn

If QSyncEn = 1, then QSync interrupt is enabled.

ATIPSyncEn If ATIPSyncEn = 1, then ATIPSync interrupt is enabled.

LaserOnEn

If LaserOnEn = 1, then LaserOn interrupt is enabled.

LaserOffEn

If LaserOffEn = 1, then LaserOff interrupt is enabled.

XErrorLarge

En

If BankSwitchEn = 1, then BankSwitch interrupt is enabled.

6

5

If DataNotValidEn = 1, then DataNotValid interrupt is enabled.

4

3

2

1

0

If XerrorLarge = 1, then XErrorLarge interrupt is enabled.

7

6

5

4

3

2

1

0

SReset1

BIT

SYMBOL

SReset1

DESCRIPTION

7 to 1

0

These 7 bits are reserved.

When set, synchronisation with PLUM on subcode transfer has failed; reset when

a logic 1 is written to this bit (Status2).

This bit is an active HIGH reset to the following blocks: Encoder/decoder, EFM

modulator, Encode control block, Serial input/output block and Encode subcode insert

block. The clock control, EFM PLL, tacho, motor interface and wobble interface remain

running.

Soft reset will reset the following registers: EFMPresetCount, EFMModulateConfig,

EFMModulateConfig2, EncodeXOffset, EncodeWriteControl, EncodeStartOffset,

EncodeStopOffset, SubPresetCount, SubConfig1, Subconfig2, SubStartData, SubData,

InputConfig, DecoMode, Output1, Output2 and Output3.

A soft reset is mandatory in the following cases:

1.

After programming the BCLK clock

2.

When switching from encode to decode

3.

When switching from decode to encode.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SAA7705H | Car radio Digital Signal Processor(DSP)(車載電臺數(shù)字信號處理器) |

| SAA7712H | Sound effects DSP(聲音效應(yīng)數(shù)字信號處理器) |

| SAA7712 | Sound effects DSP |

| SAA8110G | Digital Signal Processor (DSP) for cameras(應(yīng)用于照相中的數(shù)字信號處理器) |

| SAA8122A | Digital Still Camera Processor (ImagIC family)(數(shù)字靜態(tài)照相處理器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SAA7392HL | 制造商:NXP Semiconductors 功能描述:CD-ROM INTERFACE, 80 Pin, Plastic, QFP |

| SAA7500 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Digital satellite radio broadcasting tuner decoder SAT-2 |

| SAA7501WP | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ARD/ZDF NR.3R1 DIGITAL DECODER|LDCC|68PIN|PLASTIC |

| SAA-75J2.5-1 | 制造商:Amphenol Corporation 功能描述: |

| SAA7704H/204 | 制造商:NXP Semiconductors 功能描述:Electronic Component |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。