- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄372063 > RJ80530LZ800512 Microprocessor PDF資料下載

參數(shù)資料

| 型號(hào): | RJ80530LZ800512 |

| 元件分類(lèi): | 微處理器 |

| 英文描述: | Microprocessor |

| 中文描述: | 微處理器 |

| 文件頁(yè)數(shù): | 34/89頁(yè) |

| 文件大小: | 1672K |

| 代理商: | RJ80530LZ800512 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)當(dāng)前第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)

Mobile Intel

Pentium

III Processor-M Datasheet

34

Datasheet

298340-002

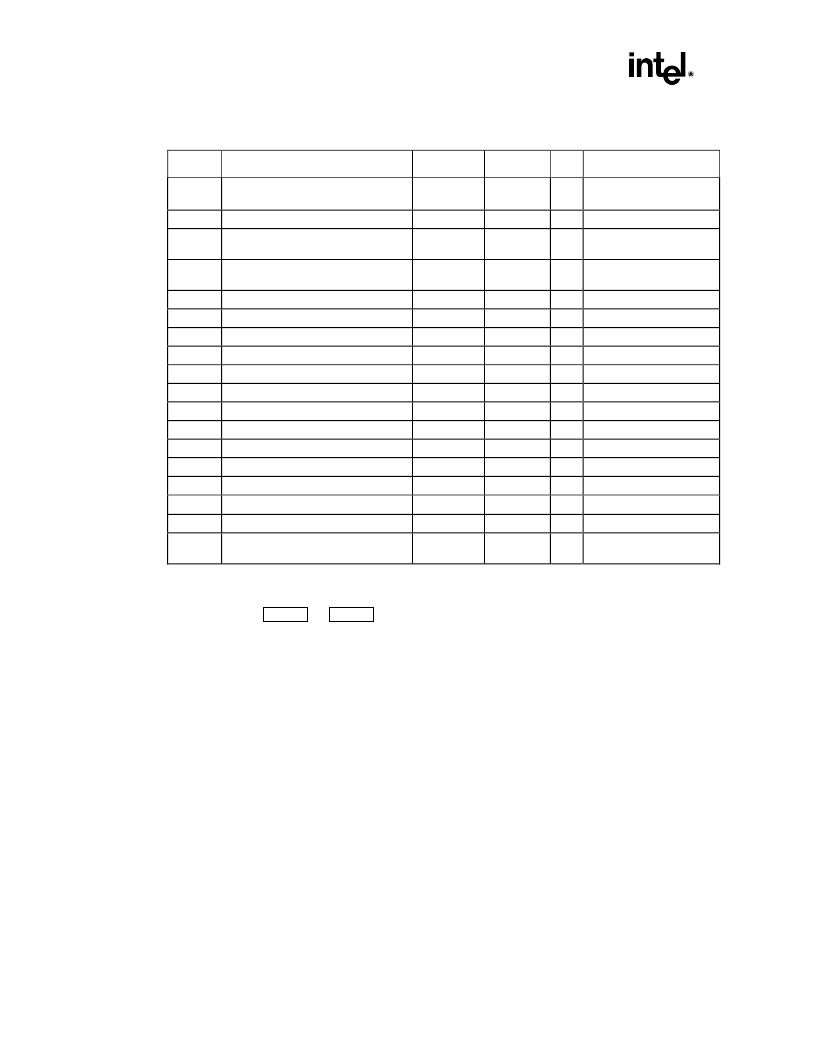

Table 18. CLKREF, APIC, TAP, CMOS, and Open-drain Signal Group DC Specifications

Symbol

Parameter

Min

Max

Unit

Notes

V

IL15

Input Low Voltage, 1.5V CMOS

–0.15

V

– 300 mV

V

V

IL18

Input Low Voltage, 1.8V CMOS

–0.36

0.36

V

Notes 1, 2

V

IH15

Input High Voltage, 1.5V CMOS

V

CMOSREFmax

+

250 mV

2.0

V

Note 11

V

IH15PICD

Input High Voltage, 1.5V PICD[1:0]

V

+

200 mV

2.0

V

Note 12

V

IH18

Input High Voltage, 1.8V CMOS

1.44

2.0

V

Notes 1, 2

V

OH15

Output High Voltage, 1.5V CMOS

N/A

1.615

V

All outputs are Open-drain

V

OH33

Output High Voltage, 3.3V signals

2.0

3.465

V

3.3V + 5%

V

OL33

Output Low Voltage, 3.3V signals

0.8

V

V

OL

Output Low Voltage

0.3

V

Note 9

V

CMOSREF

CMOSREF Voltage

0.90

1.10

V

Note 4

V

CLKREF

CLKREF Voltage

1.187

1.312

V

Note 10

V

ILVTTPWR

Input Low Voltage, VTTPWRGD

0.4

V

Note 7

V

IHVTTPWR

Input High Voltage, VTTPWRGD

1.0

V

Note 7

V

ILGHI

Input Low Voltage, GHI#

0.2

V

Note 8

V

IHGHI

Input High Voltage, GHI#

1.0

V

Note 8

R

ON

30

mA

Note 3

I

OL

Output Low Current

10

Note 6

I

L

Leakage Current for Inputs, Outputs

and I/Os

±100

μ

A

Note 5

NOTES:

1.

Parameter applies to the PWRGOOD signal only.

2.

V

and V

only apply when BCLK, BCLK# and PICCLK are stopped. PICCLK should be stopped in the

low state. See Table 30 and Table 31 for DC levels when BCLK and BCLK# are stopped.

3.

Measured at 9 mA.

4.

V

should be created from a stable 1.5V supply using a voltage divider. It must track the voltage supply

to maintain noise immunity. The same 1.5V supply should be used to power the chipset CMOS I/O buffers that

drive these signals.

5.

(0

≤

VIN/OUT

≤

V

IHx,max

).

6.

Specified as the minimum amount of current that the output buffer must be able to sink. However, V

OL,max

cannot

be guaranteed if this specification is exceeded.

7.

Parameter applies to VTTPWRGD signal only.

8.

Parameter applies to GHI# signal only.

9.

Applies to non-AGTL signals except BCLK, PWRGOOD, PICCLK, BSEL[1:0], VID[4:0].

10. ±5% DC tolerance. CLKREF must be generated from the same 2.5V supply used to generate the BCLK signal.

AC Tolerance must be less than -40dB at 1 MHz. The CLKREF DC spec only applies to platforms supporting

single-ended clocking.

11. Applies to all TAP and CMOS signals (not to APIC signals).

12. Applies to PICD[1:0].

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RJ80530MY650256 | MICROPROCESSOR|32-BIT|CMOS|BGA|479PIN|CERAMIC |

| RJ80530NZ001256 | Microprocessor |

| RJ80530VY700256 | Microprocessor |

| RJ80530VZ733256 | Microprocessor |

| RHFL4913 | THREE-TERMINAL POSITIVE FIXED VOLTAGE REGULATORS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| RJ80530LZ866512 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| RJ80530LZ933512 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| RJ80530LZ933512S L68W | 制造商:Intel 功能描述:MPU Pentium? III Processor-M 64-Bit 0.13um 933MHz 479-Pin uFCBGA |

| RJ80530LZ933512S L6AT | 制造商:Intel 功能描述:MPU Pentium? III Processor-M 64-Bit 0.13um 933MHz 479-Pin uFCBGA |

| RJ80530MY650256 | 制造商:Rochester Electronics LLC 功能描述:MOBILE CELERON 650 MHZ 256K OD 1.14V UFCBGA - Bulk |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。