- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄367854 > PDI1394L41 (NXP Semiconductors N.V.) Content Protection AV Link Layer(內(nèi)容可保護(hù)的AV鏈接層控制器) PDF資料下載

參數(shù)資料

| 型號(hào): | PDI1394L41 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | Content Protection AV Link Layer(內(nèi)容可保護(hù)的AV鏈接層控制器) |

| 中文描述: | 影音內(nèi)容保護(hù)鏈路層(內(nèi)容可保護(hù)的視聽鏈接層控制器) |

| 文件頁數(shù): | 70/81頁 |

| 文件大?。?/td> | 303K |

| 代理商: | PDI1394L41 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁當(dāng)前第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁

Philips Semiconductors

Preliminary specification

PDI1394L41

1394 content protection AV link layer controller

2000 Apr 15

67

13.5

The following registers are defined in the indirect address space. Access to these registers must be made through the Indirect Address

(INDADDR) and Indirect Data (INDDATA) registers.

Indirect Address Registers

13.5.1

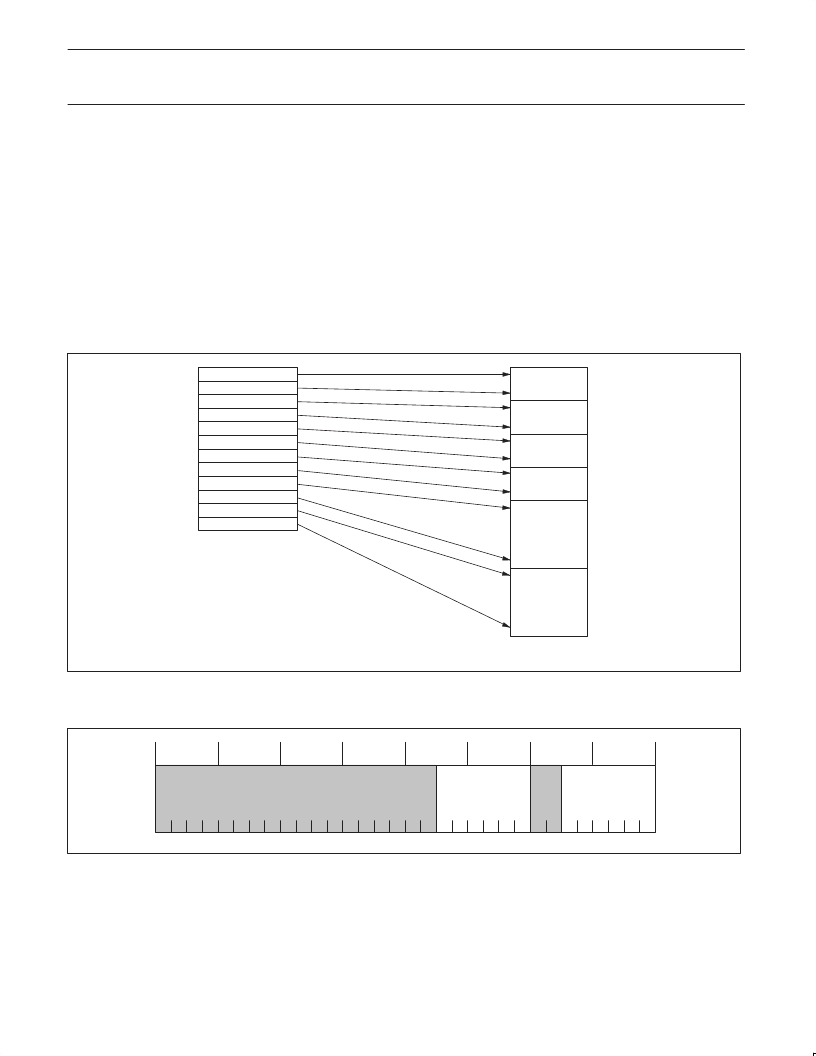

Each FIFO can be programmed to a certain size with a granularity of 64 quadlets. The size is determined by the values of the base_fifo and

end_fifo fields of the FIFO Size registers. The following formula applies:

Registers for FIFO Size Programming

fifo_size = (end_fifo – base_fifo + 1)

×

64 quadlets

The FIFO’s have been implemented on a single memory. The base_fifo and end_fifo fields are sued to determine the physical start and end

address of each FIFO inside the memory.

The start address of a FIFO is {fifo_addr[11:6] = base_fifo, fifo_addr[5:0] = 000000}.

The end address of a FIFO is {fifo_addr[11:6] = end_fifo, fifo_addr[5:0] = 111111}.

Note:

The end_fifo must be larger than base_fifo and the hardware does not check for invalid values.

000000

RRSP

000011

000100

RREQ

000111

001000

TRSP

001011

001100

TRSP

001111 & 111111

010000

IRX

011111

100000 & 000000

ITX

101111

fifo_bank

RRSPSIZE: base_fifo

RRSPSIZE: end_fifo

RREQSIZE: base_fifo

RREQSIZE: end_fifo

TRSPSIZE: base_fifo

TRSPSIZE: end_fifo

TREQSIZE: base_fifo

TREQSIZE: end_fifo

IRXSIZE: base_fifo

IRXSIZE: end_fifo

ITXSIZE: base_fifo

ITXSIZE: end_fifo

Fields in FIFO Size registers

SV01765

Figure 34.

Reset situation of size programmable FIFOs

13.5.1.1

Asynchronous Receive Response FIFO Size (RRSPSIZE) – Indirect Address: 0x100

SV01766

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11

10

9

8

7

6

5

4

3

2

1

0

base_fifo

end_fifo

0

0

0

0

0

0

0

0

0

0

1

1

Reset Value 0x00000003

Bit 31..14

Bit 13..8

Bit 7, 6

Bit 5..0

R/W

R/W

R/W

R/W

Unused bits read ‘0’

base_fifo: Base address of the FIFO

Unused bits read ‘0’

end_fifo: End address of the FIFO

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PDI1394P21 | 3-port Physical Layer Interface(三端口物理層接口) |

| PDI1394P22 | 3-port Physical Layer Interface(三端口物理層接口) |

| PDI1394P24 | 2-port 400 Mbps physical layer interface(2端口 400 Mbps物理層接口) |

| PDI40C1D00 | |

| PDI40C1300 | |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PDI1394L41BE | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:1394 content protection AV link layer controller |

| PDI1394P11 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:3-port physical layer interface |

| PDI1394P11A | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:3-port physical layer interface |

| PDI1394P11ABD | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:3-port physical layer interface |

| PDI1394P11ABD-S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Transceiver |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。