- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98023 > ML53812-2 (OKI ELECTRIC INDUSTRY CO LTD) SPECIALTY MICROPROCESSOR CIRCUIT, PQFP176 PDF資料下載

參數(shù)資料

| 型號: | ML53812-2 |

| 廠商: | OKI ELECTRIC INDUSTRY CO LTD |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | SPECIALTY MICROPROCESSOR CIRCUIT, PQFP176 |

| 封裝: | LQFP-176 |

| 文件頁數(shù): | 54/64頁 |

| 文件大小: | 668K |

| 代理商: | ML53812-2 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁當前第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁

s ML53812-2 s ––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––

54

Oki Semiconductor

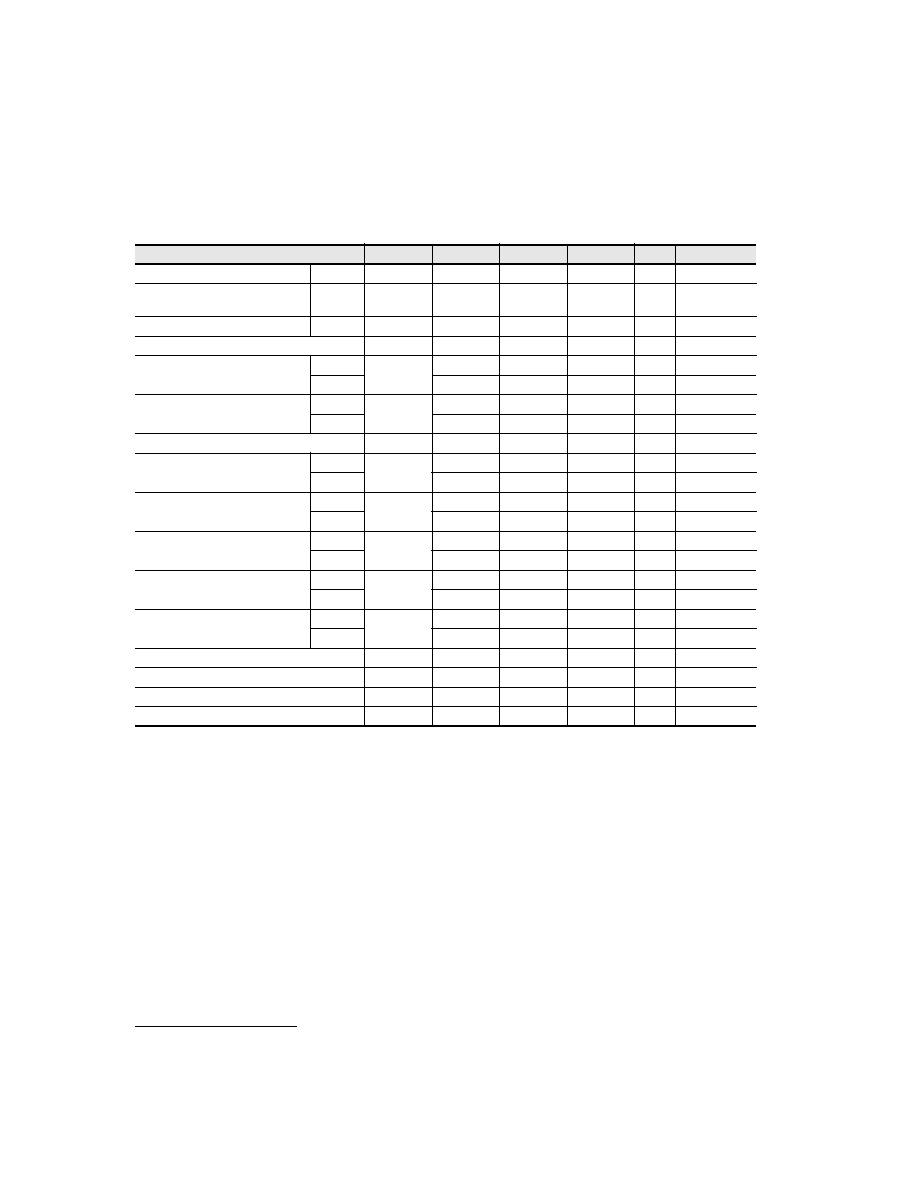

7.5 H.100/H.110 Bus Timing Specication

(Extract from H.100/H.110 Specifications, Rev. 1.0)

Parameter

Symbol

Min

Typ

Max

Unit

Notes

Clock edge rate (All Clocks)

H.100

0.25

2

V/ns

[1]

1.

The rise and fall times are determined by the edge rate in V/nS. A maximum edge rate is the fastest rate at which a clock transitions.

CT_C8_(A/B) and CT_FRAME_(A/B)_N

edge rate

H.110

0.25

2

V/ns

CT_NETREF edge rate

H.110

0.3

V/ns

[2]

2.

10% - 90%. Test Load = 150 pF.

Clock CT_C8_(A/B) Period

Tc8p

122.066-

Φ

122.074+

Φ

ns

[3]

3.

Tc8p Min and Max are under free-run conditions assuming ±32 ppm clock accuracy.

Clock CT_C8_(A/B) High Time

H.100

Tc8h

49-

Φ

73+

Φ

ns

[4]

4.

Non-cumulative, Tc8p requirements still need to be met.

H.110

63-

Φ

69+

Φ

ns

[4] [5]

5.

Duty Cycle measured at transmitter under no load conditions.

Clock CT_C8_(A/B) Low Time

H.100

Tc8l

49-

Φ

73+

Φ

ns

H.110

63-

Φ

69+

Φ

ns

Data Sample Point

Tsamp

90

ns

[6]

6.

For reference only

Data Output to HiZ Time

H.100

Tdoz

-20

0

ns

[7] [8] [9]

7.

Test Load - 200 pF

8.

Measured at the transmitter.

9.

Tdoz and Tzdo apply at every time-slot boundary.

H.110

-10

0

ns

[8] [9] [10]

10. Test Load - 12 pF

Data HiZ to Output Time

H.100

Tzdo

0

22

ns

H.110

0

11

ns

Data Output Delay Time

H.100

Tdod

0

22

ns

H.110

0

11

ns

Data Valid Time

H.100

Tdv

0

69

ns

[7] [11] [12]

11. Measured at the receiver.

12. Reference only: Tdv = Max. clock cable delay + Max. data cable delay + Max. data HiZ to output time = 12nS + 35nS + 22 nS = 69nS. Max. clock

cable delay and max. data cable delay are worst case numbers based on electrical simulation.

H.110

0

83

ns

[11] [13] [14]

13. Reference only: Tdv = Max. clock backplane delay + Max. data backplane delay + Max. data HiZ to output time = 26nS + 46nS + 11nS = 83nS. Max.

clock delay and max. data delay are worst case numbers based on electrical simulation.

14. Based on worst case electrical simulation.

Data Invalid Time

H.100

Tdiv

102

112

ns

H.110

102

112

ns

[15] [16]

15. This range accounts for

Φ (Phase Correction).

16. Tcell = Max. clock backplane delay + Max. data backplane delay + Max. Tzdo + (Min. Tdiv - Max. Tdv) + Max Tdoz + F = 26nS + 46nS + 11nS +

(102nS - 83nS) + 10nS + 10nS = 122nS. Max. clock delay and max. data delay are worst case numbers based on electrical simulation.

CT_FRAME_(A/B)_N Width

Tfp

90

122

180

ns

CT_FRAME_(A/B)_N Setup Time

Tfs

45

90

ns

CT_FRAME_(A/B)_N Hold Time

Tfh

45

90

ns

Phase Correction

Φ

010

ns

[17]

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ML54051 | FLASH MEMORY DRIVE CONTROLLER, PQFP120 |

| ML60851CGA | UNIVERSAL SERIAL BUS CONTROLLER, PQFP44 |

| ML60851DTB | UNIVERSAL SERIAL BUS CONTROLLER, PQFP44 |

| ML60852A | UNIVERSAL SERIAL BUS CONTROLLER, PQFP44 |

| ML63187-XXXGA | 4-BIT, MROM, 2 MHz, MICROCONTROLLER, PQFP128 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ML53812-2TC | 制造商:ROHM Semiconductor 功能描述: |

| ML53FAD | 制造商:MTRONPTI 制造商全稱:MTRONPTI 功能描述:Micropower CMOS Oscillators |

| ML53FAG | 制造商:MTRONPTI 制造商全稱:MTRONPTI 功能描述:Micropower CMOS Oscillators |

| ML53FCD | 制造商:MTRONPTI 制造商全稱:MTRONPTI 功能描述:Micropower CMOS Oscillators |

| ML53FCG | 制造商:MTRONPTI 制造商全稱:MTRONPTI 功能描述:Micropower CMOS Oscillators |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。