- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄299434 > M470T2953CZ3-CE7 128M X 64 DDR DRAM MODULE, 0.4 ns, ZMA200 PDF資料下載

參數(shù)資料

| 型號(hào): | M470T2953CZ3-CE7 |

| 元件分類(lèi): | DRAM |

| 英文描述: | 128M X 64 DDR DRAM MODULE, 0.4 ns, ZMA200 |

| 封裝: | ROHS COMPLIANT, SODIMM-200 |

| 文件頁(yè)數(shù): | 4/20頁(yè) |

| 文件大小: | 355K |

| 代理商: | M470T2953CZ3-CE7 |

第1頁(yè)第2頁(yè)第3頁(yè)當(dāng)前第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)

Rev. 1.6 March 2007

SODIMM

DDR2 SDRAM

Page 12 of 20

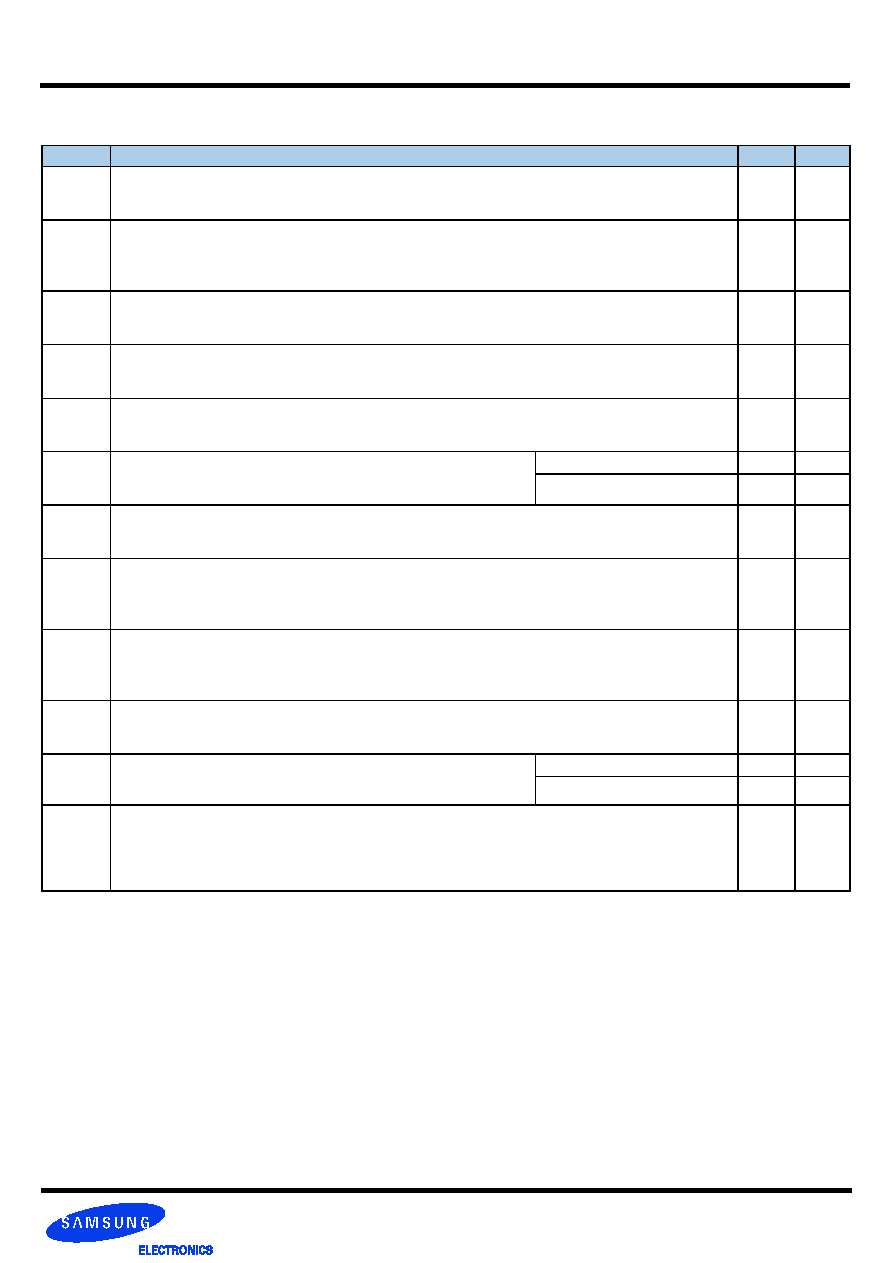

(IDD values are for full operating range of Voltage and Temperature)

Symbol

Proposed Conditions

Units

Notes

IDD0

Operating one bank active-precharge current;

tCK = tCK(IDD), tRC = tRC(IDD), tRAS = tRASmin(IDD); CKE is HIGH, CS\ is HIGH between valid commands;

Address bus inputs are SWITCHING; Data bus inputs are SWITCHING

mA

IDD1

Operating one bank active-read-precharge current;

IOUT = 0mA; BL = 4, CL = CL(IDD), AL = 0; tCK = tCK(IDD), tRC = tRC (IDD), tRAS = tRASmin(IDD), tRCD =

tRCD(IDD); CKE is HIGH, CS\ is HIGH between valid commands; Address bus inputs are SWITCHING; Data pattern

is same as IDD4W

mA

IDD2P

Precharge power-down current;

All banks idle; tCK = tCK(IDD); CKE is LOW; Other control and address bus inputs are STABLE; Data bus inputs are

FLOATING

mA

IDD2Q

Precharge quiet standby current;

All banks idle; tCK = tCK(IDD); CKE is HIGH, CS\ is HIGH; Other control and address bus inputs are STABLE; Data

bus inputs are FLOATING

mA

IDD2N

Precharge standby current;

All banks idle; tCK = tCK(IDD); CKE is HIGH, CS\ is HIGH; Other control and address bus inputs are SWITCHING;

Data bus inputs are SWITCHING

mA

IDD3P

Active power-down current;

All banks open; tCK = tCK(IDD); CKE is LOW; Other control and address bus

inputs are STABLE; Data bus inputs are FLOATING

Fast PDN Exit MRS(12) = 0mA

mA

Slow PDN Exit MRS(12) = 1mA

mA

IDD3N

Active standby current;

All banks open; tCK = tCK(IDD), tRAS = tRASmax(IDD), tRP = tRP(IDD); CKE is HIGH, CS\ is HIGH between valid

commands; Other control and address bus inputs are SWITCHING; Data bus inputs are SWITCHING

mA

IDD4W

Operating burst write current;

All banks open, Continuous burst writes; BL = 4, CL = CL(IDD), AL = 0; tCK = tCK(IDD), tRAS = tRASmax(IDD), tRP

= tRP(IDD); CKE is HIGH, CS\ is HIGH between valid commands; Address bus inputs are SWITCHING; Data bus

inputs are SWITCHING

mA

IDD4R

Operating burst read current;

All banks open, Continuous burst reads, IOUT = 0mA; BL = 4, CL = CL(IDD), AL = 0; tCK = tCK(IDD), tRAS = tRAS-

max(IDD), tRP = tRP(IDD); CKE is HIGH, CS\ is HIGH between valid commands; Address bus inputs are SWITCH-

ING; Data pattern is same as IDD4W

mA

IDD5B

Burst auto refresh current;

tCK = tCK(IDD); Refresh command at every tRFC(IDD) interval; CKE is HIGH, CS\ is HIGH between valid commands;

Other control and address bus inputs are SWITCHING; Data bus inputs are SWITCHING

mA

IDD6

Self refresh current;

CK and CK\ at 0V; CKE

≤ 0.2V; Other control and address bus inputs are

FLOATING; Data bus inputs are FLOATING

Normal

mA

Low Power

mA

IDD7

Operating bank interleave read current;

All bank interleaving reads, IOUT = 0mA; BL = 4, CL = CL(IDD), AL = tRCD(IDD)-1*tCK(IDD); tCK = tCK(IDD), tRC =

tRC(IDD), tRRD = tRRD(IDD), tFAW = tFAW(IDD), tRCD = 1*tCK(IDD); CKE is HIGH, CS\ is HIGH between valid

commands; Address bus inputs are STABLE during DESELECTs; Data pattern is same as IDD4R; Refer to the follow-

ing page for detailed timing conditions

mA

10.0 IDD Specification Parameters Definition

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M485L1624FT0-LA2 | 16M X 72 DDR DRAM MODULE, 0.75 ns, DMA200 |

| M485L1624FT0-CB3 | 16M X 72 DDR DRAM MODULE, 0.7 ns, DMA200 |

| M5-NP | UNSHIELDED, 0.056 uH - 0.12 uH, VARIABLE INDUCTOR, SMD |

| M504-7885022 | 50 CONTACT(S), MALE, RIGHT ANGLE PCMCIA CONNECTOR, SURFACE MOUNT |

| M50FLW080AN5G | 1M X 8 FLASH 3V PROM, 11 ns, PDSO40 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M470T2953CZ3-CLCC | 制造商:SAMSUNG 制造商全稱(chēng):Samsung semiconductor 功能描述:DDR2 Unbuffered SODIMM 200pin Unbuffered SODIMM based on 512Mb C-die 64bit Non-ECC |

| M470T2953CZ3-CLD5 | 制造商:SAMSUNG 制造商全稱(chēng):Samsung semiconductor 功能描述:DDR2 Unbuffered SODIMM 200pin Unbuffered SODIMM based on 512Mb C-die 64bit Non-ECC |

| M470T2953CZ3-CLE6 | 制造商:SAMSUNG 制造商全稱(chēng):Samsung semiconductor 功能描述:DDR2 Unbuffered SODIMM 200pin Unbuffered SODIMM based on 512Mb C-die 64bit Non-ECC |

| M470T2953CZ3-CLE7 | 制造商:SAMSUNG 制造商全稱(chēng):Samsung semiconductor 功能描述:DDR2 Unbuffered SODIMM 200pin Unbuffered SODIMM based on 512Mb C-die 64bit Non-ECC |

| M470T2953EZ3CE600 | 制造商:Samsung Semiconductor 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。