- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄357780 > EM6617VVVST11A 4-BIT, MROM, 0.032768 MHz, RISC MICROCONTROLLER PDF資料下載

參數(shù)資料

| 型號: | EM6617VVVST11A |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 4-BIT, MROM, 0.032768 MHz, RISC MICROCONTROLLER |

| 封裝: | STICKY TAPE |

| 文件頁數(shù): | 14/66頁 |

| 文件大小: | 759K |

| 代理商: | EM6617VVVST11A |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁當(dāng)前第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁

EM6617-1

EM Microelectronic-Marin SA , 3/99 Rev. B/258

14

7.2 Port A

The EM6617-1 has one four bit general purpose CMOS input port. The port A input can be read at any time,

internal pull-up or pull-down resistors can be chosen. All selections concerning port A are bit-wise executable.

I.e. Pull-up on PA[2], pull-down on PA[0], positive IRQ edge on PA[0] but negative on PA[1], etc.

In sleep mode the port A pull-up or pull-down resistors are turned off, and the inputs are deactivated except if

the

InpResSleep

bit in the option register

OPTFSelPB

is set to 1. In this case the port A inputs are continuously

monitored to match the input reset condition which will immediately wake the EM6617-1 from sleep mode (all

pull resistors remain).

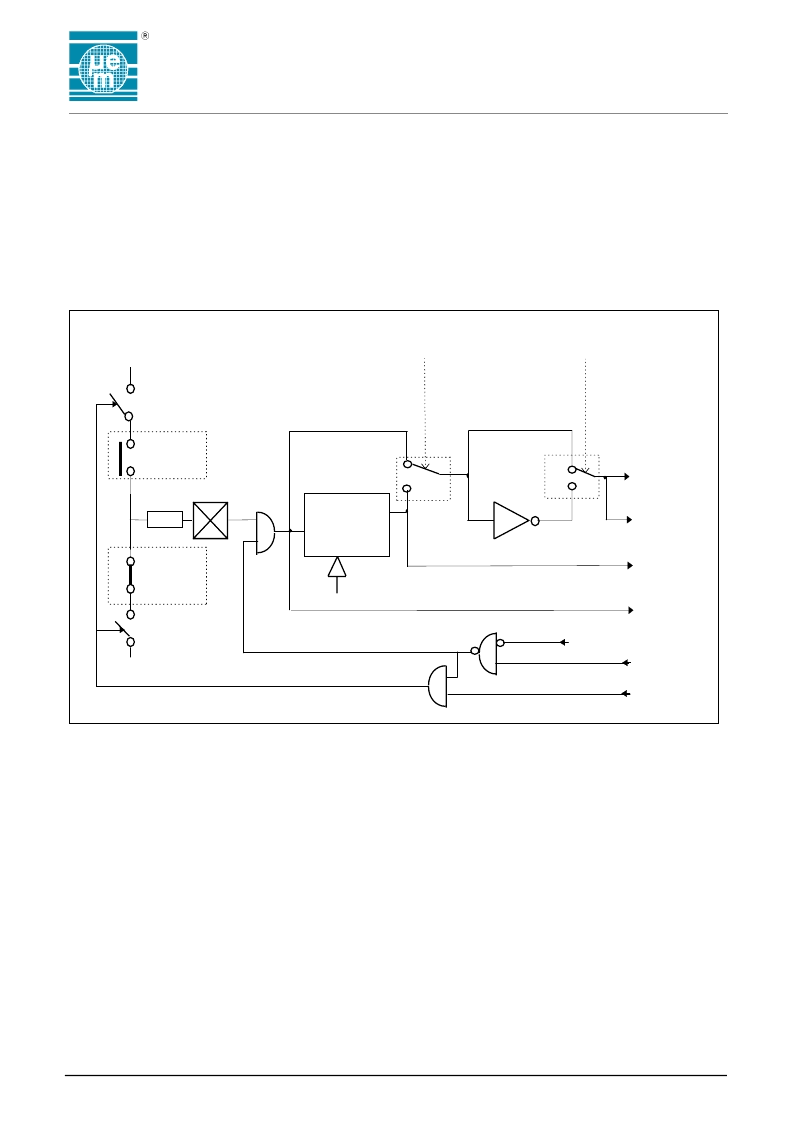

Figure 12. Input Port A Configuration

IntEdgPA[n]=0

NoDebIntPA[n]=1

Mask opt

MPAPU[n]

IRQPA[3:0]

PA[n]terminal

PA0, PA3

for 10-Bit

Counter

Mask opt

MPAPD[n]

Debouncer

μP TestVar

Ck[8] Ck[11] or

Ck[14]

DB[3:0]

NoPullPA[n]

Vbat

(V

DD

)

V

SS

Input Reset allowed

when in Sleep

Sleep

7.2.1 IRQ on Port A

For interrupt request generation (IRQ) one can choose direct or debouncer input and positive or negative edge

IRQ triggering. With the debouncer selected (

OPTDebIntPA

) the input must be stable for two rising edges of

the selected debouncer clock (

RegPresc

). This means a worst case of 16 ms (default) or 2 ms (0.25 ms by

metal mask) with a system clock of 32 KHz.

Either a positive or a negative edge on the port A inputs - after debouncer or not - can generate an interrupt

request. This selection is done in the option register

OPTIntEdgPA.

All four bits of port A can provide an IRQ, each pin with its own interrupt mask bit in the

RegIRQMask1

register.

When an IRQ occurs, inspection of the

RegIRQ1

,

RegIRQ2

and

RegIRQ3

registers allows the interrupt to be

identified and treated.

At power on or after any reset the

RegIRQMask1

is set to 0, thus disabling any input interrupt. A new interrupt is

only stored with the next active edge after the corresponding interrupt mask is cleared. See also the interrupt

chapter 13.

It is recommended to mask the port A IRQ’s while one changes the selected IRQ edge. Else one may generate

a IRQ (Software IRQ). I.e. PA[0] on ‘0’ then changing from positive to negative edge selection on PA[0] will

immediately trigger an IRQPA[0] if the IRQ was not masked.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| EMCL12M2H-187.5103MTR | CRYSTAL OSCILLATOR, CLOCK, 187.5103 MHz, LVPECL OUTPUT |

| EMDS22N2J-156.250M | CRYSTAL OSCILLATOR, CLOCK, 156.25 MHz, LVDS OUTPUT |

| EMDS23C2H-10.000M | CRYSTAL OSCILLATOR, CLOCK, 10 MHz, LVDS OUTPUT |

| EMDS23E2H-77.760MTR | CRYSTAL OSCILLATOR, CLOCK, 77.76 MHz, LVDS OUTPUT |

| EMIF4-100FCD4 | EMI FILTER/TVS ARRAY |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EM6617WP11 | 制造商:EMMICRO 制造商全稱:EM Microelectronic - MARIN SA 功能描述:Ultra Low Power Microcontroller with ADC AND EEPROM |

| EM6617WP27 | 制造商:EMMICRO 制造商全稱:EM Microelectronic - MARIN SA 功能描述:Ultra Low Power Microcontroller with ADC AND EEPROM |

| EM6617WS11 | 制造商:EMMICRO 制造商全稱:EM Microelectronic - MARIN SA 功能描述:Ultra Low Power Microcontroller with ADC AND EEPROM |

| EM6617WS27 | 制造商:EMMICRO 制造商全稱:EM Microelectronic - MARIN SA 功能描述:Ultra Low Power Microcontroller with ADC AND EEPROM |

| EM6617WW11 | 制造商:EMMICRO 制造商全稱:EM Microelectronic - MARIN SA 功能描述:Ultra Low Power Microcontroller with ADC AND EEPROM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。