- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄357780 > EM6617VVVST11A 4-BIT, MROM, 0.032768 MHz, RISC MICROCONTROLLER PDF資料下載

參數(shù)資料

| 型號: | EM6617VVVST11A |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 4-BIT, MROM, 0.032768 MHz, RISC MICROCONTROLLER |

| 封裝: | STICKY TAPE |

| 文件頁數(shù): | 10/66頁 |

| 文件大小: | 759K |

| 代理商: | EM6617VVVST11A |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁當前第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁

EM6617-1

EM Microelectronic-Marin SA , 3/99 Rev. B/258

10

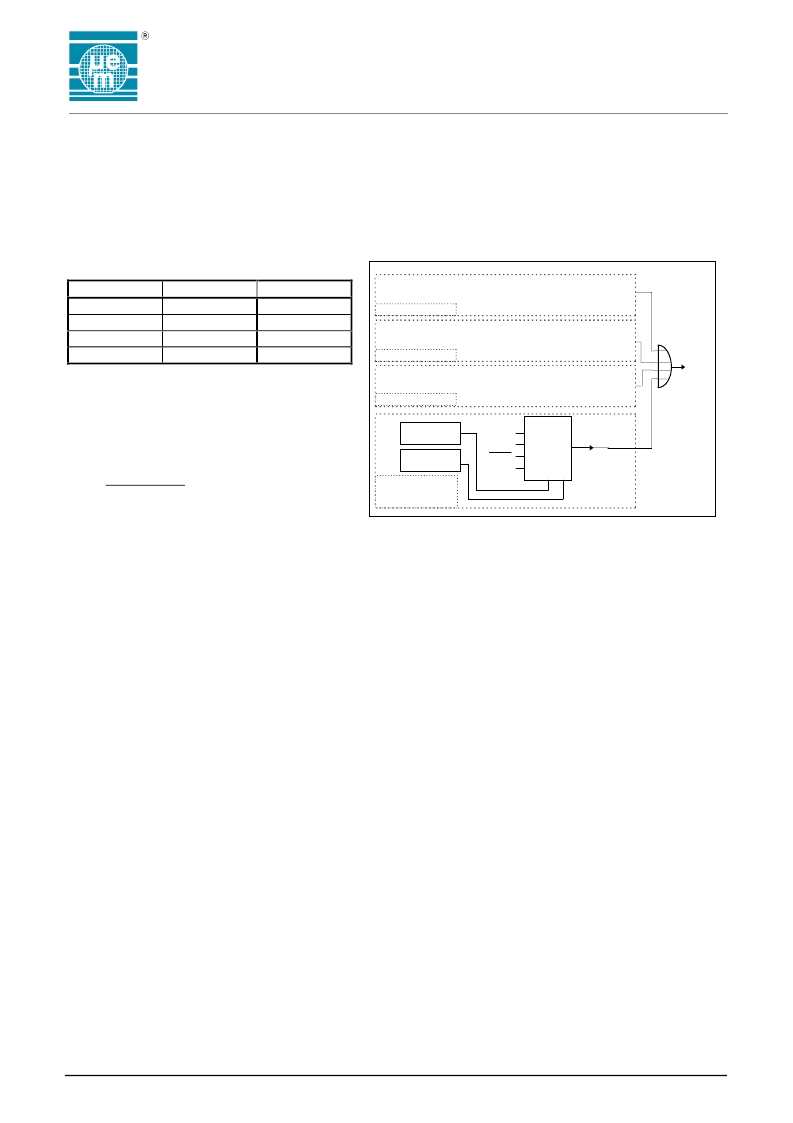

5.3.2 OR -Type Reset function

If wanted, needs to be chosen with the metal 1 option settings. Any one of the port A inputs can trigger a reset.

Following formula is applicable :

InpResPA

=

InpResPA[0]

+

InpResPA[1]

+

InpResPA[2]

+

InpResPA[3]

InpRes1PA[n]

0

0

1

1

n = 0 to 3

InpRes2PA[n]

0

1

0

1

InpResPA[n]

V

SS

PA[n]

not PA[n]

V

DD

i.e. ; - no reset if all InpResPA[n] = V

SS

.

- Don’t care function on a single bit with

its InpResPA[n] = Vss.

- Always Reset if any InpResPA[3:0] = V

DD

5.4 Digital Watchdog Timer Reset

The digital watchdog is a simple, non-programmable, 2-bit timer, that counts on each rising edge of Ck[1]. It will

generate a system reset if it is not periodically cleared. The watchdog timer function can be inhibited by

activating an inhibit digital watchdog bit (

NoLogicWD

) located in

RegSysCntl3

. At power up, and after any

system reset, the watchdog timer is activated.

If for any reason the CPU stops, then the watchdog timer can detect this situation and activate the system reset

signal. This function can be used to detect program overrun, endless loops, etc. For normal operation, the

watchdog timer must be reset periodically by software at least every 2.5 seconds (system clock = 32 KHz), or a

system reset signal is generated.

The watchdog timer is reset by writing a ‘1’ to the

WDReset

bit in the timer. This resets the timer to zero and

timer operation restarts immediately. When a ‘0’ is written to

WDReset

there is no effect. The watchdog timer

operates also in the standby mode and thus, to avoid a system reset, one should not remain in standby mode

for more than 2.5 seconds.

From a system reset state, the watchdog timer will become active after 3.5 seconds. However, if the watchdog

timer is influenced from other sources (i.e. prescaler reset), then it could become active after just 2.5 seconds. It

is therefore recommended to use the Prescaler

IRQHz1

interrupt to periodically reset the watchdog every

second.

It is possible to read the current status of the watchdog timer in

RegSysCntl2

. After watchdog reset, the

counting sequence is (on each rising edge of CK[1]) : ‘00’, ‘01’, ‘10’, ‘11’ {

WDVal1

WDVal0

}. When going into

the ‘11’ state, the watchdog reset will be active within second. The watchdog reset activates the system reset

which in turn resets the watchdog. If the watchdog is inhibited it’s timer is reset and therefore always reads ‘0’.

Figure 10. Input Port A Reset Structure

0

1 MUX

2

3 1 0

V

SS

PA[3]

PA[3]

V

DD

BIT

[0]

BIT

[1]

BIT

[2]

BIT

[3]

InpResPA

InpResPA[3]

InpRes2PA[3]

InpRes1PA[3]

Input Port A Reset

Bit[2] Selection

Input Port A Reset

Bit[1] Selection

Input Port A Reset

Bit[0] Selection

Input Port A Reset

Bit[3] Selection

Input

Reset

from

Port A

相關PDF資料 |

PDF描述 |

|---|---|

| EMCL12M2H-187.5103MTR | CRYSTAL OSCILLATOR, CLOCK, 187.5103 MHz, LVPECL OUTPUT |

| EMDS22N2J-156.250M | CRYSTAL OSCILLATOR, CLOCK, 156.25 MHz, LVDS OUTPUT |

| EMDS23C2H-10.000M | CRYSTAL OSCILLATOR, CLOCK, 10 MHz, LVDS OUTPUT |

| EMDS23E2H-77.760MTR | CRYSTAL OSCILLATOR, CLOCK, 77.76 MHz, LVDS OUTPUT |

| EMIF4-100FCD4 | EMI FILTER/TVS ARRAY |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| EM6617WP11 | 制造商:EMMICRO 制造商全稱:EM Microelectronic - MARIN SA 功能描述:Ultra Low Power Microcontroller with ADC AND EEPROM |

| EM6617WP27 | 制造商:EMMICRO 制造商全稱:EM Microelectronic - MARIN SA 功能描述:Ultra Low Power Microcontroller with ADC AND EEPROM |

| EM6617WS11 | 制造商:EMMICRO 制造商全稱:EM Microelectronic - MARIN SA 功能描述:Ultra Low Power Microcontroller with ADC AND EEPROM |

| EM6617WS27 | 制造商:EMMICRO 制造商全稱:EM Microelectronic - MARIN SA 功能描述:Ultra Low Power Microcontroller with ADC AND EEPROM |

| EM6617WW11 | 制造商:EMMICRO 制造商全稱:EM Microelectronic - MARIN SA 功能描述:Ultra Low Power Microcontroller with ADC AND EEPROM |

發(fā)布緊急采購,3分鐘左右您將得到回復。