- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1915 > DS31412N (Maxim Integrated Products)IC 12CH DS3/3 FRAMER 349-BGA PDF資料下載

參數(shù)資料

| 型號: | DS31412N |

| 廠商: | Maxim Integrated Products |

| 文件頁數(shù): | 9/89頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC 12CH DS3/3 FRAMER 349-BGA |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 控制器類型: | DS3/E3 調(diào)幀器 |

| 接口: | LIU |

| 電源電壓: | 3.135 V ~ 3.465 V |

| 電流 - 電源: | 960mA |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 349-BGA 裸露焊盤 |

| 供應(yīng)商設(shè)備封裝: | 349-HCBGA(27x27) |

| 包裝: | 托盤 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁當(dāng)前第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁

DS3146/DS3146/DS31412 6-/8-/12-Channel DS3/E3 Framers

17 of 89

6.1 Status Register Description

There are two types of bits used to build the status and information registers. The real-time status register bit

indicates the state of the corresponding signal at the time it was read. The latched status register bit is set when

the corresponding signal changes state (low-to-high, high-to-low, or both, depending on the bit). The latched status

bit is cleared when written with logic 1 and is not set again until the corresponding signal changes state again.

The following is example host-processor pseudocode that checks to see if the BERT SYNC status has changed:

If ((BSRL and 01h) neq 0) then

// SYNCL bit is set

BSRL = 01h

// Clear SYNCL bit only

If ((BSR and 01h) neq 0) then

// BERT has changed to in sync

–––––

Else

// BERT has changed to out of sync

–––––

There are four suffixes used for status and information register names: SR for real-time status registers, SRL for

latched status registers, SRIE for interrupt-enable registers, and IR for information registers. Latched status bits

have the suffix “L” and interrupt-enable bits have the suffix “IE.” The bits in the SR, SRL, and SRIE registers are

arranged such that related real-time status, latched status, and interrupt-enable bits are located in the same bit

position in neighboring registers. For example, Table 6-B shows that the real-time status bit SYNC, the latched

status bit SYNCL, and the interrupt-enable bit SYNCIE are all located in bit 0 of their respective registers (BSR,

BSRL, and BSRIE).

When set, most latched status register bits can cause an interrupt on the

INT pin if the corresponding interrupt-

enable register bit is also set. Most latched status register bits have an associated real-time status register bit.

Information registers can contain a mix of real-time and latched status bits, none of which can cause an interrupt.

Table 6-B. Status Register Set Example

REGISTER

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

N/A

RA1

RA0

N/A

BBCO

BECO

SYNC

N/A

RA1L

RA0L

BEDL

BBCOL

BECOL

SYNCL

N/A

BEDIE

BBCOIE

BECOIE

SYNCIE

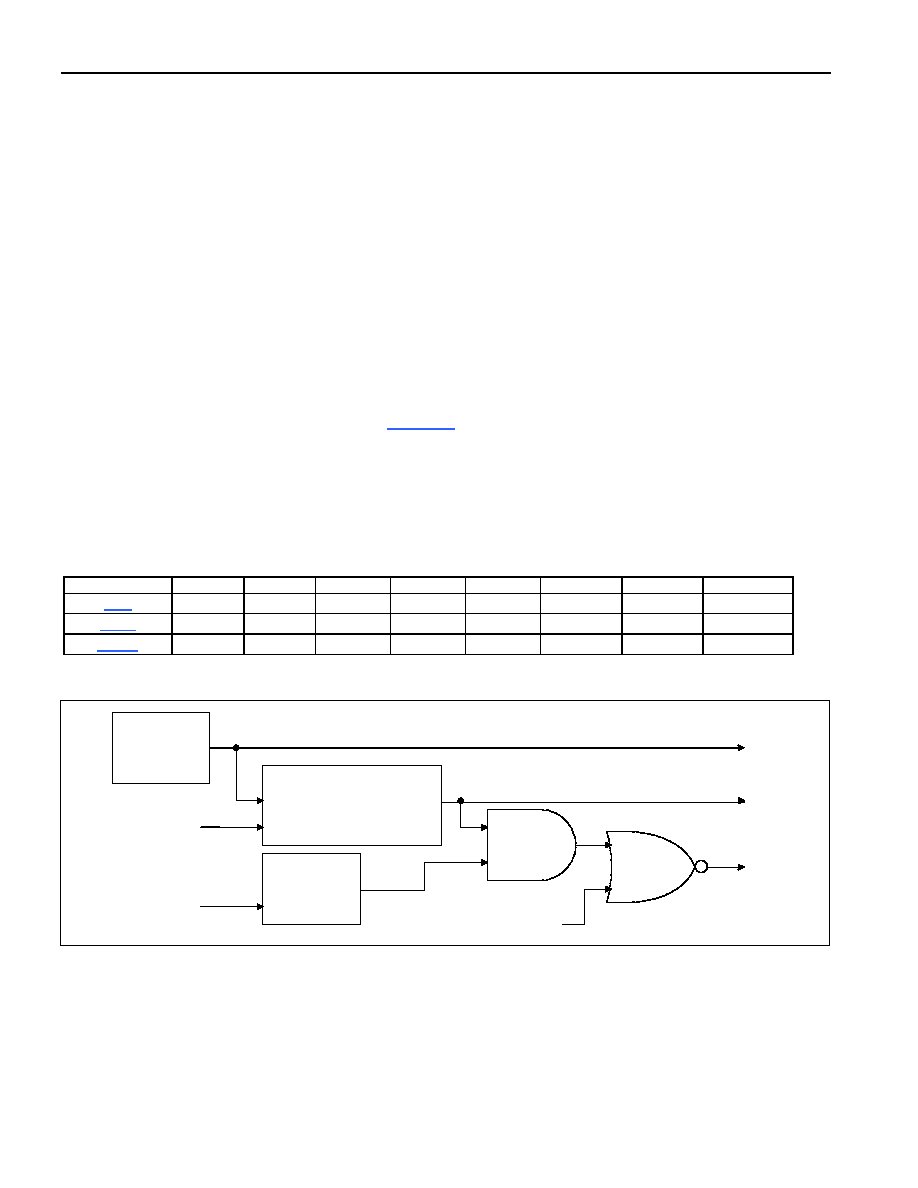

Figure 6-1. Status Register Interrupt Flow

WR

EVENT

LATCHED STATUS REGISTER

SET ON EVENT DETECT

CLEAR ON WRITE LOGIC 1

INT ENABLE

REGISTER

SR

SRL

INT

OTHER INT

SOURCE

REAL-TIME STATUS

LATCHED STATUS

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DS3150TN | IC LIU T3/E3/STS-1 IND 48-TQFP |

| DS3154N+ | IC LIU DS3/E3/STS-1 QD 144CSBGA |

| DS3164+ | IC ATM/PACKET PHY QUAD 400-BGA |

| DS3170+ | IC TXRX DS3/E3 100-CSBGA |

| DS3172N+ | IC TXRX DS3/E3 DUAL 400-BGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DS31415 | 制造商:MAXIM 制造商全稱:Maxim Integrated Products 功能描述:3-Input, 4-Output, Single DPLL Timing IC with Sub-ps Output Jitter and 1588 Clock |

| DS31415_1107 | 制造商:MAXIM 制造商全稱:Maxim Integrated Products 功能描述:3-Input, 4-Output, Single DPLL Timing IC with Sub-ps Output Jitter and 1588 Clock |

| DS31415DK | 功能描述:網(wǎng)絡(luò)開發(fā)工具 DS31415 Dev Kit RoHS:否 制造商:Rabbit Semiconductor 產(chǎn)品:Development Kits 類型:Ethernet to Wi-Fi Bridges 工具用于評估:RCM6600W 數(shù)據(jù)速率:20 Mbps, 40 Mbps 接口類型:802.11 b/g, Ethernet 工作電源電壓:3.3 V |

| DS31415GN+ | 制造商:Microsemi Corporation 功能描述:SINGLE DPLL TIMING IC W/APLL & 1588 CLOCK - Rail/Tube 制造商:Zarlink Semiconductor Inc 功能描述:SINGLE DPLL TIMING IC W/APLL & 1588 CLOCK - Rail/Tube 制造商:Microsemi 功能描述:DPLL 256-Pin CSBGA |

| DS3141N | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC Single DS3/E3 Framer RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。