- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄375384 > AX88796BLI (ASIX Electronics Corporation) Low-pin-count Non-PCI 8/16-bit 10/100M Fast Ethernet Controller PDF資料下載

參數(shù)資料

| 型號: | AX88796BLI |

| 廠商: | ASIX Electronics Corporation |

| 英文描述: | Low-pin-count Non-PCI 8/16-bit 10/100M Fast Ethernet Controller |

| 中文描述: | 低引腳數(shù)的非PCI 16位產(chǎn)品10/100M自適應(yīng)快速以太網(wǎng)控制器 |

| 文件頁數(shù): | 77/82頁 |

| 文件大?。?/td> | 519K |

| 代理商: | AX88796BLI |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁當(dāng)前第77頁第78頁第79頁第80頁第81頁第82頁

ASIX ELECTRONICS CORPORATION

77

AX88796BLF / AX88796BLI

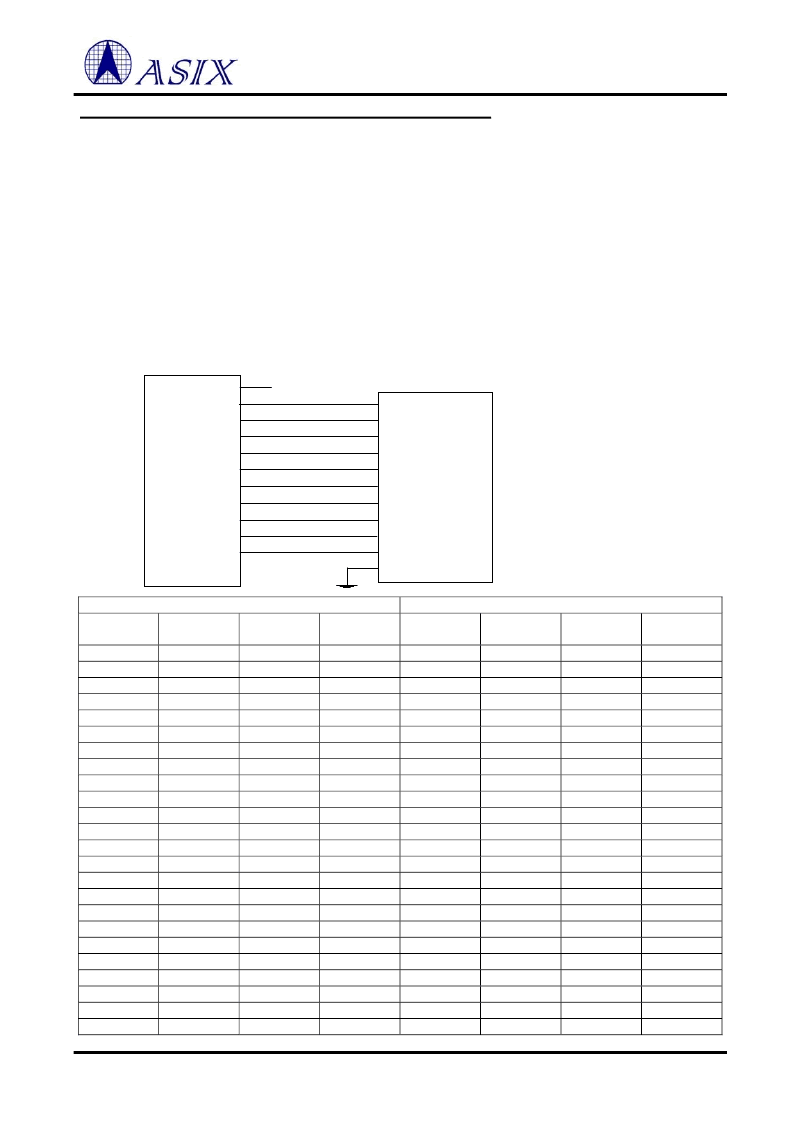

Appendix A4: co-work with 32-bit processor

An example, AX88796B co-work with Samsung 2440 processor. (32-bit processor with external 16-bit bus)

AX88796B’s bus setting as ISA mode. (Without external resister connect to EECS and EECK) Host can use burst

read mode, it is useful host processor increment its address when moving AX88796B received data.

AX88796B supports two kinds of Data Port for receiving/transmitting packets from/to AX88796B. One is the PIO

Data Port (offset 10h); the other one is the SRAM-like Data Port (e.g. offset 800h ~ FFFh for Samsung2440

processor as described in below figure). The SRAM-like Data Port address range depends on which address line of

host processor is being connected to the address line SA5/FIFO_SEL of AX88796B.

Software on host CPU can issue Single Data Read/Write command to both PIO Data Port and SRAM-like Data Port.

However, to use Burst Data Read/Write commands, one has to use SRAM-like Data Port, which requires

SA5/FIFO_SEL (pin 45) of AX88796B connecting to an upper address line of host CPU. AX88796B with Samsung

2440 processor reference schematic has SA5/FIFO_SEL pin connected to upper address line (i.e. A11 of Samsung

2440) for supporting Burst Data Read/Write commands.

Read

Host Addr

A[11:0]

CSR Offset

0

Offset 1

Offset 0

0

2

Offset 1

Offset 1

1

4

Offset 3

Offset 2

2

6

Offset 3

Offset 3

3

8

Offset 5

Offset 4

4

A

Offset 5

Offset 5

5

C

Offset 7

Offset 6

6

E

Offset 7

Offset 7

7

10

Offset 9

Offset 8

8

12

Offset 9

Offset 9

9

14

Offset B

Offset A

A

16

Offset B

Offset B

B

18

Offset D

Offset C

C

1A

Offset D

Offset D

D

1C

Offset F

Offset E

E

1E

Offset F

Offset F

F

20

10 (DP)

10 (DP)

10 (DP)

22

X

X

X

24

Offset 13

Offset 12

12

26

Offset 13

Offset 13

13

28

Offset 15

Offset 14

14

2A

Offset 15

Offset 15

15

2C

Offset 17

Offset 16

16

2E

Offset 17

Offset 17

17

Write

SD[15:8]

SD[7:0]

AX88796B

Host Addr

A[11:0]

0

2

4

6

8

A

C

E

10

12

14

16

18

1A

1C

1E

20

22

24

26

28

2A

2C

2E

SD[15:8]

SD[7:0]

AX88796B

CSR Offset

0

1

2

3

4

5

6

7

8

9

A

B

C

D

E

F

10 (DP)

X

no effect

no effect

no effect

no effect

no effect

no effect

no effect

no effect

no effect

no effect

no effect

no effect

no effect

no effect

no effect

no effect

10 (DP)

X

no effect

no effect

no effect

no effect

no effect

no effect

To Offset 0

To Offset 1

To Offset 2

To Offset 3

To Offset 4

To Offset 5

To Offset 6

To Offset 7

To Offset 8

To Offset 9

To Offset A

To Offset B

To Offset C

To Offset D

To Offset E

To Offset F

10 (DP)

X

To Offset 12 12

To Offset 13 13

To Offset 14 14

To Offset 15 15

To Offset 16 16

To Offset 17 17

A0

A1

A2

A3

A4

A5/FIFO_SEL

CSn

RDn

WRn

IRQ

AEN/PSEN

A0

A1

A2

A3

A4

A5

A11

CSn

RDn

WRn

INT

Samsung2440

AX88796B

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AX88872P | 10/100BASE Dual Speed “Swipeater” Controller |

| AX9902MS | 2N and 2P-Channel Enhancement Mode Power MOSFET |

| AX9902MSA | 2N and 2P-Channel Enhancement Mode Power MOSFET |

| AXC-051 | ACTIVE FILTER FOR RIPPLE ATTENUATION 5A |

| AXC-051-R | ACTIVE FILTER FOR RIPPLE ATTENUATION 5A |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AX88796C | 制造商:ASIX 制造商全稱:ASIX 功能描述:Low-Power SPI or Non-PCI Ethernet Controller |

| AX88796CLF | 制造商:ASIX Electronics Corporation 功能描述: |

| AX88796L | 制造商:ASIX 制造商全稱:ASIX 功能描述:3-in-1 Local Bus Fast Ethernet Controller |

| AX88796LF | 制造商:ASIX 功能描述:10/100 MAC |

| AX88850 | 制造商:ASIX 制造商全稱:ASIX 功能描述:100BASE-TX/FX Repeater Controller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。