- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄375249 > AD9888 (Analog Devices, Inc.) 100/140/170/205 MSPS Analog Flat Panel Interface PDF資料下載

參數(shù)資料

| 型號(hào): | AD9888 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | 100/140/170/205 MSPS Analog Flat Panel Interface |

| 中文描述: | 100/140/170/205 MSPS的模擬平板顯示接口 |

| 文件頁(yè)數(shù): | 2/32頁(yè) |

| 文件大?。?/td> | 249K |

| 代理商: | AD9888 |

第1頁(yè)當(dāng)前第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)

REV. A

–2–

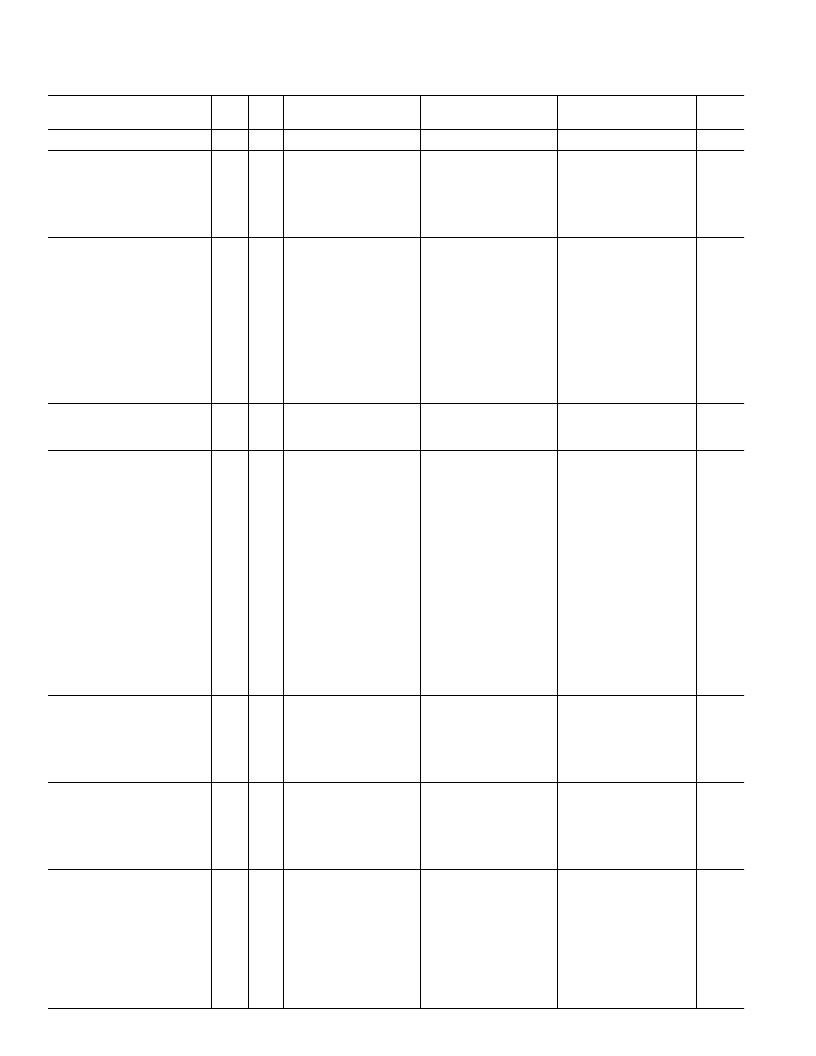

AD9888–SPECIFICATIONS

(V

D

= 3.3 V, V

DD

= 3.3 V, ADC Clock = Maximum Conversion Rate)

Test

AD9888KS-100/-140

1

Typ

AD9888KS-170

Typ

AD9888KS-205

Typ

Parameter

Temp Level Min

Max

Min

Max

Min

Max

Unit

RESOLUTION

8

8

8

Bits

DC ACCURACY

Differential Nonlinearity

25

°

C

Full

25

°

C

Full

25

°

C

I

VI

I

VI

I

±

0.5

+1.25/–1.0

+1.35/–1.0

±

2.0

±

2.5

±

0.6

+1.25/–1.0

+1.50/–1.0

±

0.8

+1.50/–1.0

+1.80/–1.0

±

3.75

±

4.25

LSB

LSB

LSB

LSB

Integral Nonlinearity

±

0.5

±

0.75

±

2.25

±

1.0

±

2.75

No Missing Codes

Guaranteed

Guaranteed

Guaranteed

ANALOG INPUT

Input Voltage Range

Minimum

Maximum

Gain Tempco

Input Bias Current

25

°

C

25

°

C

25

°

C

25

°

C

Full

Full

Full

Full

Full

Full

I

I

V

IV

IV

V

IV

VI

VI

VI

0.5

0.5

0.5

V p-p

V p-p

ppm/

°

C

μ

A

μ

A

pF

M

mV

% FS

% FS

1.0

1.0

1.0

100

100

100

1

2

1

2

1

2

Input Capacitance

Input Resistance

Input Offset Voltage

Input Full-Scale Matching

Offset Adjustment Range

3

3

3

1

1

1

7

2.5

49

90

9.0

53

7

2.5

49

90

9.0

53

7

2.5

49

90

9.0

53

44

44

44

REFERENCE OUTPUT

Output Voltage

Temperature Coefficient

Full

Full

VI

V

1.20

1.25

±

50

1.30

1.20

1.25

±

50

1.30

1.20

1.25

±

50

1.30

V

ppm/

°

C

SWITCHING PERFORMANCE

Maximum Conversion Rate

Minimum Conversion Rate

Data to Clock Skew

t

BUFF2

t

STAH2

t

DHO2

t

DAL2

t

DAH2

t

DSU2

t

STASU2

t

STOSU2

HSYNC Input Frequency

Maximum PLL Clock Rate

Minimum PLL Clock Rate

PLL Jitter

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

25

°

C

Full

Full

VI

IV

IV

VI

VI

VI

VI

VI

VI

VI

VI

IV

VI

IV

IV

IV

IV

100/140

170

205

MSPS

MSPS

ns

μ

s

μ

s

μ

s

μ

s

μ

s

ns

μ

s

μ

s

kHz

MHz

MHz

ps p-p

ps p-p

ps/

°

C

10

+1.25

10

+1.25

10

+1.25

–1.25

4.7

4.0

0

4.7

4.0

250

4.7

4.0

15

100/140

–1.25

4.7

4.0

0

4.7

4.0

250

4.7

4.0

15

170

–1.25

4.7

4.0

0

4.7

4.0

250

4.7

4.0

15

205

110

110

110

10

700

3

1000

3

10

700

4

1000

4

10

700

4

1000

4

470

450

440

Sampling Phase Tempco

15

15

15

DIGITAL INPUTS

Input Voltage, High (V

IH

)

Input Voltage, Low (V

IL

)

Input Current, High (I

IH

)

Input Current, Low (I

IL

)

Input Capacitance

Full

Full

Full

Full

25

°

C

VI

VI

IV

IV

V

2.5

2.5

2.5

V

V

μ

A

μ

A

pF

0.8

–1.0

+1.0

0.8

–1.0

+1.0

0.8

–1.0

+1.0

3

3

3

DIGITAL OUTPUTS

Output Voltage, High (V

OH

)

Output Voltage, Low (V

OL

)

Duty Cycle

DATACK,

DATACK

Output Coding

Full

Full

VI

VI

V

D

– 0.1

V

D

– 0.1

V

D

– 0.1

V

V

0.1

0

.1

0.1

Full

IV

44

49

55

44

49

55

44

49

55

%

Binary

Binary

Binary

POWER SUPPLY

V

D

Supply Voltage

V

DD

Supply Voltage

P

VD

Supply Voltage

I

D

Supply Current (V

D

)

I

DD

Supply Current (V

DD

)

5

IP

VD

Supply Current (P

VD

)

Total Power Dissipation

Power-Down Supply Current

Power-Down Dissipation

Full

Full

Full

25

°

C

25

°

C

25

°

C

Full

Full

Full

IV

IV

IV

V

V

V

VI

VI

VI

3.0

2.2

3.0

3.3

3.3

3.3

200

50

8

850

12

40

3.6

3.6

3.6

3.0

2.2

3.0

3.3

3.3

3.3

215

55

9

920

12

40

3.6

3.6

3.6

3.0

2.2

3.0

3.3

3.3

3.3

230

60

10

990

12

40

3.6

3.6

3.6

V

V

V

mA

mA

mA

mW

mA

mW

1050

20

66

1150

20

66

1250

20

66

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD9888KS-100 | 100/140/170/205 MSPS Analog Flat Panel Interface |

| AD9888KS-140 | TRI N PLUG F 2-13 |

| AD9888KS-170 | TRI N RECP M FLG 2-13 |

| AD9888KS-205 | TRI N RECP M J/N 2-13 |

| AD9891 | CCD Signal Processors with Precision Timing⑩ Generator |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD9888/PCB | 制造商:AD 制造商全稱:Analog Devices 功能描述:100/140/170/205 MSPS Analog Flat Panel Interface |

| AD9888_11 | 制造商:AD 制造商全稱:Analog Devices 功能描述:100 MSPS/140 MSPS/170 MSPS Analog Flat Panel Interface |

| AD98888KS | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| AD9888KS-100 | 制造商:Analog Devices 功能描述:ADC Triple 100Msps 8-bit Parallel 128-Pin MQFP 制造商:Rochester Electronics LLC 功能描述:100 MHZ ANALOG GRAPHICS INTERFACE CHIP - Bulk |

| AD9888KS-140 | 制造商:Rochester Electronics LLC 功能描述:140MHZ ANALOG GRAPHICS INTERFACE CHIP - Bulk 制造商:Analog Devices 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。