- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄16986 > XRD98L63ZEVAL (Exar Corporation)EVAL BOARD FOR XRD98L63 PDF資料下載

參數(shù)資料

| 型號(hào): | XRD98L63ZEVAL |

| 廠商: | Exar Corporation |

| 文件頁數(shù): | 13/41頁 |

| 文件大小: | 0K |

| 描述: | EVAL BOARD FOR XRD98L63 |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 系列: | * |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁當(dāng)前第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁

XRD98L63

20

Rev.1.01

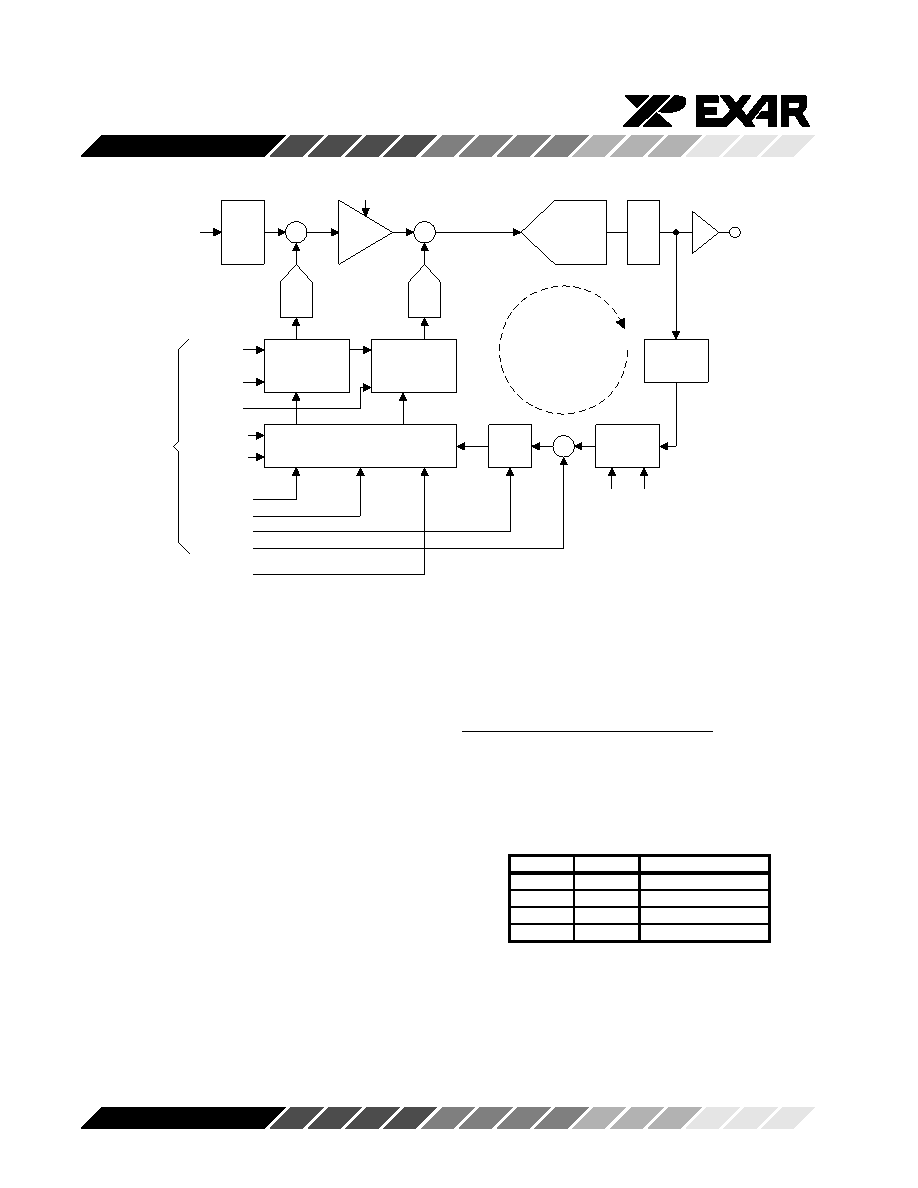

CDS

12-bit ADC

Hot Pixel

C lipper

Pixel

Averager

+

-

+

Even & Odd

Coarse

Accumulators

Even & Odd

Fine

Accumulators

Offset Calibration Logic

PGA

Reg

Hold

OB[7:0]

Gain[9:0]

DB[11:0]

CDAC

FDAC

+

B lack Level

O ffset Calibration

Loop

DNS[1:0]

ManCAL

CDE, CDO

From Serial

Interface

Registers

CCD

signal

W L[11:0]

Mode

DNS

Filter

FDE, FDO

OBL[11:0]

Gain[9:0]

Avg[1:0]

OBdel[2:0]

From Gain Logic

Figure 12. Detailed Block Diagram of the Black Level Offset Calibration Logic

Offset Difference

Next, the Offset register value, OB[7:0], is subtracted

from the OB pixel average. If the difference is positive,

the offset DACs are adjusted to reduce the effective

ADC output code. If the difference is negative, the

offset DACs are adjusted to increase the effective ADC

output code. The DNS option will affect how the DAC

adjustments are made.

Coarse & Fine Accumulators

The Coarse and Fine Accumulators are the registers

which hold the digital codes for the Coarse and Fine

Offset DACs. The Offset DAC adjustments are made

by adding to or subtracting from the value in the Fine

accumulator. If there is an overflow or underflow in the

Fine Accumulator, the Fine Accumulator is reset to it’s

mid-scale value, and the Coarse Accumulator is

incremented or decremented accordingly.

In the Multiple Gain Mode, there are separate accumu-

lators for even and odd lines.

DNS[1]

DNS[0]

DNS Filter Width

0

OFF

0

1

Narrow (default)

1

0

Medium

1

Wide

Calibration Options

Digital Noise Suppression (DNS) Filter

The purpose of this option is to eliminate small

changes in the Black Level offset by making the

calibration system less sensitive to small changes in

the measured offset. In this mode, the user has the

option of selecting from three filter settings, see Table 5.

Table 5. DNS Threshold Programming

To activate the Digital Noise Suppression mode, write

to the DNS[1:0] bits in the Calibration register.

By default, the Digital Noise Suppression is ON and set

to the narrow filter width.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RCB13DHLN | CONN EDGECARD 26POS DIP .050 SLD |

| P1330R-104K | INDUCTOR POWER 100.0UH SMD |

| VI-270-EY | CONVERTER MOD DC/DC 5V 50W |

| 0210490388 | CABLE JUMPER 1.25MM .030M 32POS |

| VE-20X-EY | CONVERTER MOD DC/DC 5.2V 50W |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XRDAN27 | 制造商:EXAR 制造商全稱:EXAR 功能描述:Compensating for Zero Order Hold Effects |

| XRDAN28 | 制造商:EXAR 制造商全稱:EXAR 功能描述:Frequency Response Effects of Overampling and Averaging on A/D Output Data |

| XRDAN29 | 制造商:EXAR 制造商全稱:EXAR 功能描述:Criteria for Accurate Sampling of Analog Signals |

| XRDAN30 | 制造商:EXAR 制造商全稱:EXAR 功能描述:CMOS Current Output D/A Converter Design Concepts for Wide Bandwidth Applications |

| XR-E | 制造商:CREE 制造商全稱:Cree, Inc 功能描述:XLamp XR-E and XR-C LED Binning and Labeling |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。