- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98083 > SME5434PCI-440 64-BIT, 440 MHz, RISC PROCESSOR, XMA PDF資料下載

參數(shù)資料

| 型號: | SME5434PCI-440 |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 64-BIT, 440 MHz, RISC PROCESSOR, XMA |

| 封裝: | 130 X 100 MM, 45 MM HEIGHT MODULE |

| 文件頁數(shù): | 23/30頁 |

| 文件大?。?/td> | 393K |

| 代理商: | SME5434PCI-440 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁當前第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁

3

360/440MHz CPU; 0.25 to 2 MB L2 cache; UPA64S, 66MHz PCI Interfaces

UltraSPARC IIi CPU Module

September 2001

Sun Microsystems, Inc

SME5431PCI-360

SME5434PCI-440

Preliminary

Component Overview

The UltraSPARC IIi 360 MHz CPU module and the UltraSPARC IIi 440 MHz CPU module consist of the fol-

lowing components.

UltraSPARC-IIi Processor in a ceramic LGA package

One cache tag SRAM and two cache data SRAMs

Clock generator, divider, and buffer ICs

PCI/JTAG/temperature sense interface connector

Memory/UPA64S interface connector

UltraSPARC-IIi CPU

The UltraSPARC-IIi CPU is a high-performance, highly-integrated, superscalar processor implementing the

SPARC V9 64-bit RISC architecture. This CPU can sustain the execution of up to four instructions per cycle

even in the presence of conditional branches and cache misses. It supports a 44-bit virtual address space and

a 41-bit physical address space. The instruction set also includes the VIS Instruction Set that accommodates

the functions:

most common operations related to two-dimensional image processing

three-dimensional graphics

video compression and decompression and other pixel-based algorithms

support for high-bandwidth bcopy through block-load and block-store instructions

The SME1430LGA CPU is contained in a 587-pin 1.27 mm-pitch ceramic LGA package of dimensions 37.5 mm

by 37.5 mm. This package is the same as that used for the SME1040LGA CPU.

The PCI interface supports the PCI 2.1 specication with a 66-MHz clock rate or a 33-MHz rate across a

PCI bridge, for example the Advanced PCI Bridge (APB), part number SME2411BGA-66. PCI DMA trans-

fers become cache coherent after they are presented to the CPU.

External (L2) Cache

The L2 cache is connected to the L2-cache data bus and is implemented in three synchronous SRAM ICs.

The CPU-SRAM interface runs at half of the CPU pipeline frequency (for example, 220 MHz for the 440 MHz

CPU). SRAM signals operate at 1.9-V, pseudo-HSTL levels. The SRAM clock is a differential, pseudo HSTL

signal.

For the 440 MHz UltraSPARC IIi CPU Modules, the external-cache SRAM interfaces operate in 2–2, regis-

ter-latch mode, which means that it takes two processor clocks to send the address and access the SRAM

array, and two clocks to return the data. The 2–2 mode has a four cycle pin-to-pin latency and provides the

highest performance SRAM solution at a given frequency.

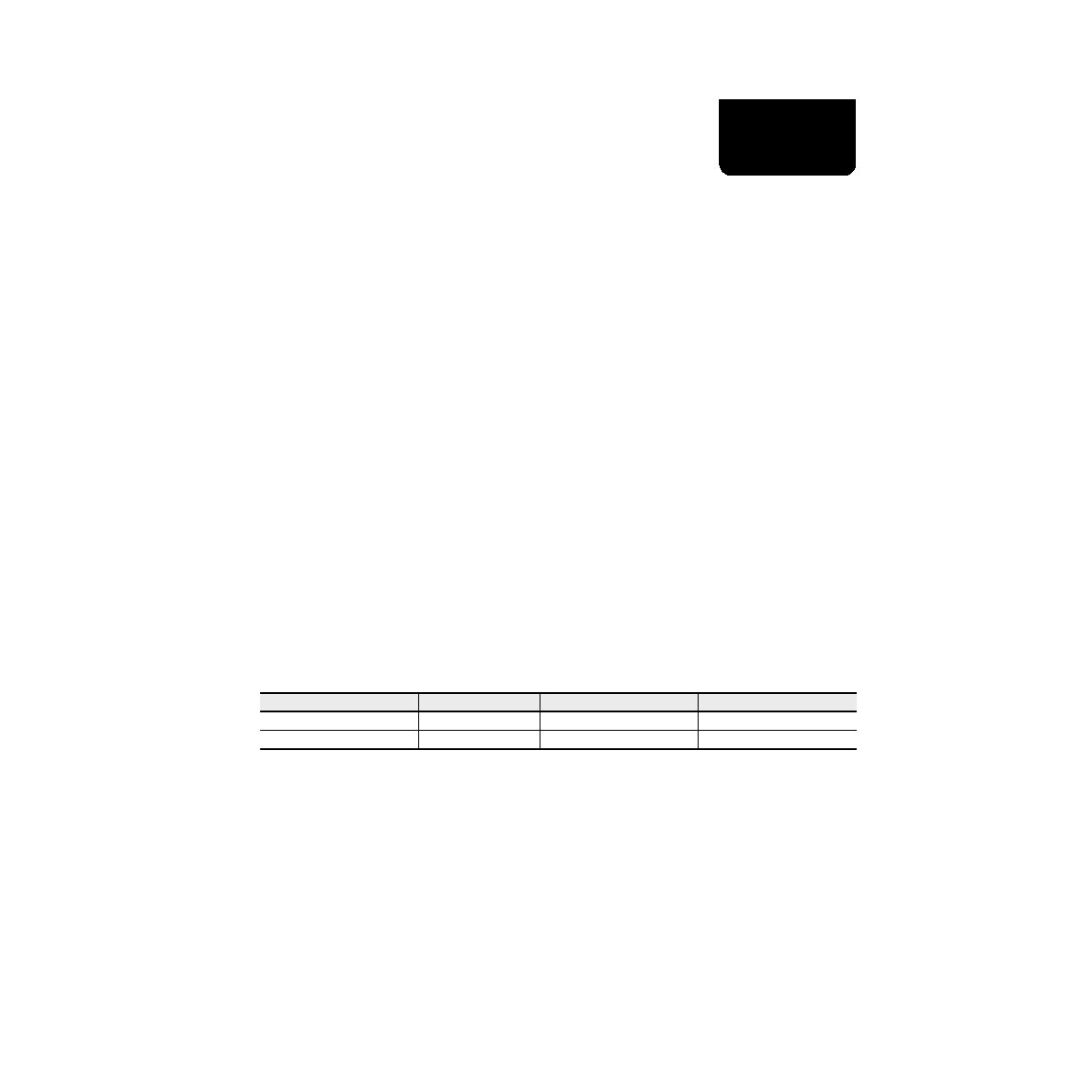

L2-Cache SRAM Detail

Module Part No.

Data Cache Size

One Cache Tag SRAM

Two Cache Data SRAMs [1]

1. Congured on a 64-bit data + 8-bit parity interface

SME5431PCI-360

0.25 megabyte

64K x 18 bit

32K x 36 bit

SME5434PCI-440

2.0 megabyte

256K x 18 bit

256K x 36 bit

相關PDF資料 |

PDF描述 |

|---|---|

| SME5434PCI-480 | 64-BIT, 480 MHz, RISC PROCESSOR, XMA |

| SMFR-29C516ESC | 16-BIT ERROR DETECT AND CORRECT CKT, QFP100 |

| SMJ320C26FJ | 16-BIT, 40 MHz, OTHER DSP, CQCC68 |

| SMJ320C31KGDM40B | 32-BIT, 40 MHz, OTHER DSP, UUC132 |

| SMJ320C40KGDS50C | 32-BIT, 50 MHz, OTHER DSP, UUC325 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| S-ME6 | 制造商:Phoenix Contact 功能描述:Lock, switching, ME terminal |

| SME6.3T471M8X16LL | 制造商:Texas Instruments 功能描述:EA471-6R3M85 |

| SME6.3VB101M6X11LL | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MINIATURE, GENERAL PURPOSE, SOLVENT PROOF |

| SME6.3VB102M10X12LL | 制造商:United Chemi-Con Inc 功能描述:Capacitor, Aluminium, 1mf, 6.3V, 20±% |

| SME6.3VB103M16X31LL | 功能描述:鋁質電解電容器 - 帶引線 10KuF 6.3V RoHS:否 制造商:Kemet 引線類型: 電容:220 uF 容差:20 % 電壓額定值:25 V 工作溫度范圍: 端接類型:Radial 外殼直徑:8 mm 外殼長度:11 mm 引線間隔:5 mm 產(chǎn)品:General Purpose Electrolytic Capacitors 封裝:Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復。