- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383804 > SCANPSC100FSC (FAIRCHILD SEMICONDUCTOR CORP) Embedded Boundary Scan Controller (IEEE 1149.1 Support) PDF資料下載

參數(shù)資料

| 型號: | SCANPSC100FSC |

| 廠商: | FAIRCHILD SEMICONDUCTOR CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | Embedded Boundary Scan Controller (IEEE 1149.1 Support) |

| 中文描述: | SPECIALTY MICROPROCESSOR CIRCUIT, PDSO28 |

| 封裝: | 0.300 INCH, MS-013, SOIC-28 |

| 文件頁數(shù): | 5/21頁 |

| 文件大小: | 208K |

| 代理商: | SCANPSC100FSC |

5

www.fairchildsemi.com

S

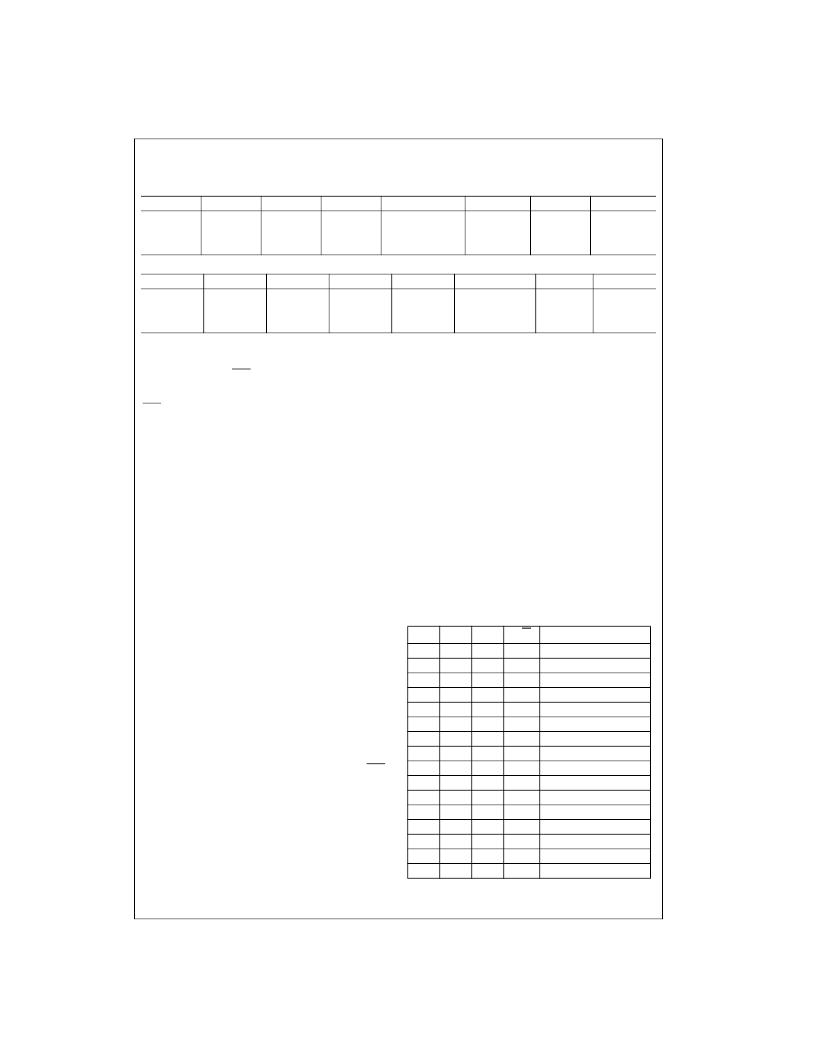

Mode and Status Registers

(Continued)

MODE REGISTER 2 (MODE2)

Write:

Read:

This register contains both mode and status bits. Bits 4

–

7

are status bits only. Bit 3 is a status bit during read opera-

tions and a mode bit during write operations. Bits 0

–

2 are

mode bits only. Upon RST low, or a synchronous reset, the

value placed in MODE2 is 10111000 (Read mode). Latches

used to update status bits 3

–

7 retain their last state upon

RST and are in an

“

unknown

”

state after power-up. To ini-

tialize the latches to a known state, they need to be

updated using the Update Status bit (bit 2) or continuous

update bit (bit 3).

Bit 7:

Set high if the TDO shifter/buffer is not full,

i.e., one or both 8-bit TDO FIFOs are ready to

be written to.

Bit 6:

Set high if the TDI shifter/buffer is not empty,

i.e., one or both 8-bit TDI FIFOs are ready to

be read from.

Bit 5:

Set high if the 32-bit counter has not been

loaded, or has reached terminal count.

Bit 4:

Set high if the TMS0 shifter/buffer is not full,

i.e., one or both 8-bit TMS0 FIFOs are ready

to be written to.

Bit 3

(Read Cycle):

Set high if the TMS1 shifter/buffer is not full,

i.e., one or both 8-bit TMS1 FIFOs are ready

to be written to.

Bit 3

(Write Cycle):

If set, will cause all status bits to be continu-

ously updated.

Bit 2

(Read Cycle):

Shows the state of the Continuous Update bit

during read operations (Bit 3 during writes).

Bit 2

(Write Cycle):

If set, will cause a pulse to be issued internally

that will update all status bits. This bit will be

reset upon completion of the pulse. The state

of this bit is not readable. It is reset upon RST

low.

Bit 1:

If set, will cause a synchronous reset of all

functions except the parallel interface. The

value of this bit will return to zero when the

reset operation is complete.

Bit 0:

If set, will cause the 32-bit counter to count for

one SCK cycle (no TCK cycle will be gener-

ated). The value of this bit will return to zero

when the single step operation is complete.

PROGRAMMING RESTRICTIONS

Because certain mode bits enable shift operations for cer-

tain functions, these mode bits should

not

be changed

when shift operations are in progress. The alignment of all

registers during shift operations is controlled by a 3-bit

counter in the TCK control block. Enabling or disabling a

function in the middle of a shift operation may disrupt the

logic necessary to keep all shifter/buffers byte-aligned.

For example, if the TDO shifter/buffer (already loaded) is

enabled while the 3-bit counter value is 3, the shifter/buffer

will only shift out only five bits of the first byte loaded.

The following bits should not be changed when shift opera-

tions are in progress, i.e., when TCK is enabled (see sec-

tion on TCK Control).

MODE0(7:3)

MODE1(4:3)

MODE2(0)

Parallel Processor Interface (PPI)

ADDRESS ASSIGNMENT

The following table defines which register is selected for

access with the address lines, A(2:0).

Bit 7

Not

Used

Bit 6

Not

Used

Bit 5

Not

Used

Bit 4

Not

Used

Bit 3

Bit 2

Update

Status

Bit 1

Bit 0

Single

Step

CNT32

Continuous

Update

Reset

Bit 7

TDO

Status

Bit 6

TDI

Status

Bit 5

CNT32

Status

Bit 4

TMS0

Status

Bit 3

TMS1

Status

Bit 2

Bit 1

Bit 0

Single

Step

CNT32

Continuous

Update

Reset

A2

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

A1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

A0

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

R/W

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

Function

TDO Shifter/Buffer

Counter Register 1

TDI Shifter/Buffer

TDI Shifter/Buffer

TMS0 Shifter/Buffer

Counter Register 2

TMS1 Shifter/Buffer

Counter Register 3

32-Bit Counter

Counter Register 0

MODE0

MODE0

MODE1

MODE1

MODE2

MODE2

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SCANPSC110FSC | SCAN Bridge Hierarchical and Multidrop Addressable JTAG Port (IEEE1149.1 System Test Support) |

| SCP-5453 | SOCKET,IC,16PIN,MACHINE TOOLED WIRE WRAP,0.3"WIDE,0.515"LEAD |

| SCP-6122 | POWER OPERATIONAL AMPLIFIER |

| SCS152 | HM Series Hermetically Sealed Basic Switch, Single Pole Double Throw Circuitry, 0.5 A at 28 Vdc, Integral Lever Actuator, Solder Termination |

| SCS152-IS | Small glass bead with axial leads |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SCANPSC100FSCX | 功能描述:接口 - 專用 Emb Boun Scan Cont RoHS:否 制造商:Texas Instruments 產(chǎn)品類型:1080p60 Image Sensor Receiver 工作電源電壓:1.8 V 電源電流:89 mA 最大功率耗散: 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:BGA-59 |

| SCANPSC110 | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:SCAN Bridge Hierarchical and Multidrop Addressable JTAG Port (IEEE1149.1 System Test Support) |

| SCANPSC110_ZFC3026B WAF | 制造商:Fairchild Semiconductor Corporation 功能描述: |

| SCANPSC110F | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:SCAN Bridge Hierarchical and Multidrop Addressable JTAG Port (IEEE1149.1 System Test Support) |

| SCANPSC110FDMQB | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:SCAN Bridge Hierarchical and Multidrop Addressable JTAG Port (IEEE1149.1 System Test Support) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。