- 您現在的位置:買賣IC網 > PDF目錄383804 > SCANPSC100FSC (FAIRCHILD SEMICONDUCTOR CORP) Embedded Boundary Scan Controller (IEEE 1149.1 Support) PDF資料下載

參數資料

| 型號: | SCANPSC100FSC |

| 廠商: | FAIRCHILD SEMICONDUCTOR CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | Embedded Boundary Scan Controller (IEEE 1149.1 Support) |

| 中文描述: | SPECIALTY MICROPROCESSOR CIRCUIT, PDSO28 |

| 封裝: | 0.300 INCH, MS-013, SOIC-28 |

| 文件頁數: | 2/21頁 |

| 文件大小: | 208K |

| 代理商: | SCANPSC100FSC |

www.fairchildsemi.com

2

S

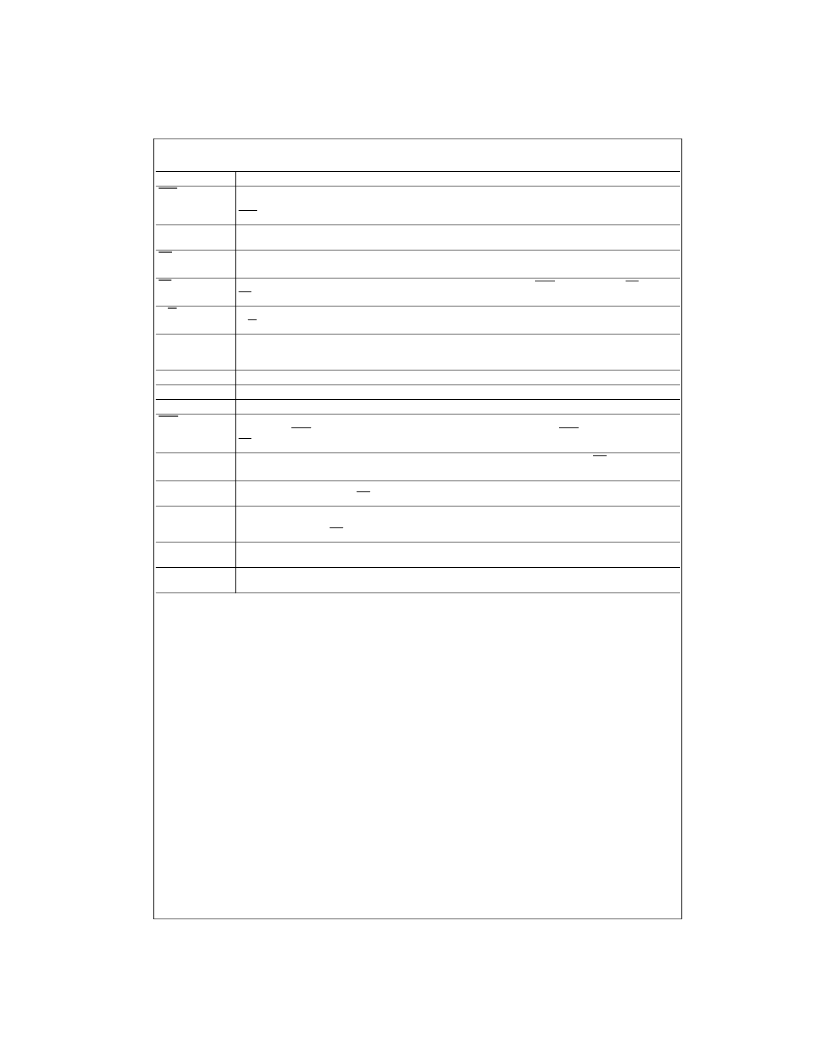

Pin Descriptions

Pin Name

Description

RST

(Input)

The Reset pin is an asynchronous input that, when LOW, initializes the SCANPSC100. Mode bits,

Shifter/Buffer and CNT32 control logic, TCK Control, and the PPI are all initialized to defined states.

RST has hysteresis for improved noise immunity.

The System Clock drives all internal timing. The test clock, TCK, is a gated and buffered version of SCK.

SCK has hysteresis for improved immunity.

SCK

(Input)

OE

(Input)

Output Enable 3-STATEs all SSI outputs when HIGH. A 20 k

pull-up resistor is connected to

automatically 3-STATE these outputs when this signal is floating.

CE

(Input)

Chip Enable, when LOW, enables the PPI for byte transfers. D(7:0) and RDY are 3-STATEd if CE is HIGH.

CE has hysteresis for improved noise immunity.

R/W (Input)

Read/Write defines a PPI cycle

—

Read when HIGH, Write when LOW.

R/W has hysteresis for improved noise immunity.

Strobe is used for timing all PPI byte transfers. D(7:0) are 3-STATEd when STB is HIGH. All other PPI

inputs must meet specified setup and hold times with respect to this signal. STB has hysteresis for noise

improved immunity.

The Address pins are used to select the register to be written to or read from.

Bidirectional pins used to transfer parallel data to and from the SCANPSC100.

Interrupt is used to trigger a host interrupt for any of the defined interrupt events. INT is active HIGH.

STB

(Input)

A(2:0)

(Input)

D(7:0) (I/O)

INT

(Output)

RDY

(3-STATE Output)

Ready is used to synchronize asynchronous byte transfers between the host and the SCANPSC100.

When LOW, RDY signals that the addressed register is ready to be accessed RDY is enabled when

CE is LOW

TDO

(3-STATE Output)

TMS(1:0)

(3-STATE Output)

TCK

(3-STATE Output)

Test Data Out is the serial scan output from the SCANPSC100. TDO is enabled when OE is LOW.

The Test Mode Select pins are serial outputs used to supply control logic to the UUT.

TMS(1:0) are enabled when OE is LOW.

The Test Clock output is a buffered version of SCK for distribution in the UUT.

TCK Control logic starts and stops TCK to prevent overflow and underflow conditions.

TCK is enabled when OE is LOW.

Test Data In is the serial scan input to the SCANPSC100. A 20 k

pull-up resistor is connected to force

TDI to a logic 1 when the TDO line from the UUT is floating.

The Freeze pin is used to asynchronously generate a user-specific pulse on TCK. If the FRZ Enable Mode

bit is set, TCK will be forced HIGH if FRZ goes HIGH. FRZ has hysteresis for improved noise immunity.

TDI

(Input)

FRZ

(Input)

相關PDF資料 |

PDF描述 |

|---|---|

| SCANPSC110FSC | SCAN Bridge Hierarchical and Multidrop Addressable JTAG Port (IEEE1149.1 System Test Support) |

| SCP-5453 | SOCKET,IC,16PIN,MACHINE TOOLED WIRE WRAP,0.3"WIDE,0.515"LEAD |

| SCP-6122 | POWER OPERATIONAL AMPLIFIER |

| SCS152 | HM Series Hermetically Sealed Basic Switch, Single Pole Double Throw Circuitry, 0.5 A at 28 Vdc, Integral Lever Actuator, Solder Termination |

| SCS152-IS | Small glass bead with axial leads |

相關代理商/技術參數 |

參數描述 |

|---|---|

| SCANPSC100FSCX | 功能描述:接口 - 專用 Emb Boun Scan Cont RoHS:否 制造商:Texas Instruments 產品類型:1080p60 Image Sensor Receiver 工作電源電壓:1.8 V 電源電流:89 mA 最大功率耗散: 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:BGA-59 |

| SCANPSC110 | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:SCAN Bridge Hierarchical and Multidrop Addressable JTAG Port (IEEE1149.1 System Test Support) |

| SCANPSC110_ZFC3026B WAF | 制造商:Fairchild Semiconductor Corporation 功能描述: |

| SCANPSC110F | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:SCAN Bridge Hierarchical and Multidrop Addressable JTAG Port (IEEE1149.1 System Test Support) |

| SCANPSC110FDMQB | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:SCAN Bridge Hierarchical and Multidrop Addressable JTAG Port (IEEE1149.1 System Test Support) |

發(fā)布緊急采購,3分鐘左右您將得到回復。