- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄383804 > SCANPSC100FSC (FAIRCHILD SEMICONDUCTOR CORP) Embedded Boundary Scan Controller (IEEE 1149.1 Support) PDF資料下載

參數(shù)資料

| 型號(hào): | SCANPSC100FSC |

| 廠商: | FAIRCHILD SEMICONDUCTOR CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | Embedded Boundary Scan Controller (IEEE 1149.1 Support) |

| 中文描述: | SPECIALTY MICROPROCESSOR CIRCUIT, PDSO28 |

| 封裝: | 0.300 INCH, MS-013, SOIC-28 |

| 文件頁(yè)數(shù): | 1/21頁(yè) |

| 文件大?。?/td> | 208K |

| 代理商: | SCANPSC100FSC |

當(dāng)前第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)

2000 Fairchild Semiconductor Corporation

DS010968

www.fairchildsemi.com

December 1991

Revised May 2000

S

SCANPSC100F

Embedded Boundary Scan Controller

(IEEE 1149.1 Support)

General Description

The SCANPSC100F is designed to interface a generic par-

allel processor bus to a serial scan test bus. It is useful in

improving scan throughput when applying serial vectors to

system test circuitry and reduces the software overhead

that is associated with applying serial patterns with a paral-

lel processor. The SCANPSC100F operates by serializing

data from the parallel bus for shifting through the chain of

1149.1 compliant components (i.e., scan chain). Scan data

returning from the scan chain is placed on the parallel port

to be read by the host processor. Up to two scan chains

can be directly controlled with the SCANPSC100F via two

independent TMS pins. Scan control is supplied with user

specific patterns which makes the SCANPSC100F proto-

col-independent. Overflow and underflow conditions are

prevented by stopping the test clock. A 32-bit counter is

used to program the number of TCK cycles required to

complete a scan operation within the boundary scan chain

or to complete a SCANPSC100F Built-In Self Test (BIST)

operation. SCANPSC100F device drivers and 1149.1

embedded test application code are available with Fair-

child’s SCAN Ease software tools.

Features

I

Compatible with IEEE Std. 1149.1 (JTAG) Test Access

Port and Boundary Scan Architecture

I

Supported by Fairchild’s SCAN Ease (Embedded Appli-

cation Software Enabler) Software

I

Uses generic, asynchronous processor interface; com-

patible with a wide range of processors and PCLK fre-

quencies

I

Directly supports up to two 1149.1 scan chains

I

16-bit Serial Signature Compaction (SSC) at the Test

Data In (TDI) port

I

Automatically produces pseudo-random patterns at the

Test Data Out (TDO) port

I

Fabricated on FACT

1.5

μ

m CMOS process

I

Supports 1149.1 test clock (TCK) frequencies up to

25 MHz

I

TTL-compatible inputs; full-swing CMOS outputs with

24 mA source/sink capability

Ordering Code:

Devices also available in Tape and Reel. Specify by appending the suffix letter

“

X

”

to the ordering code.

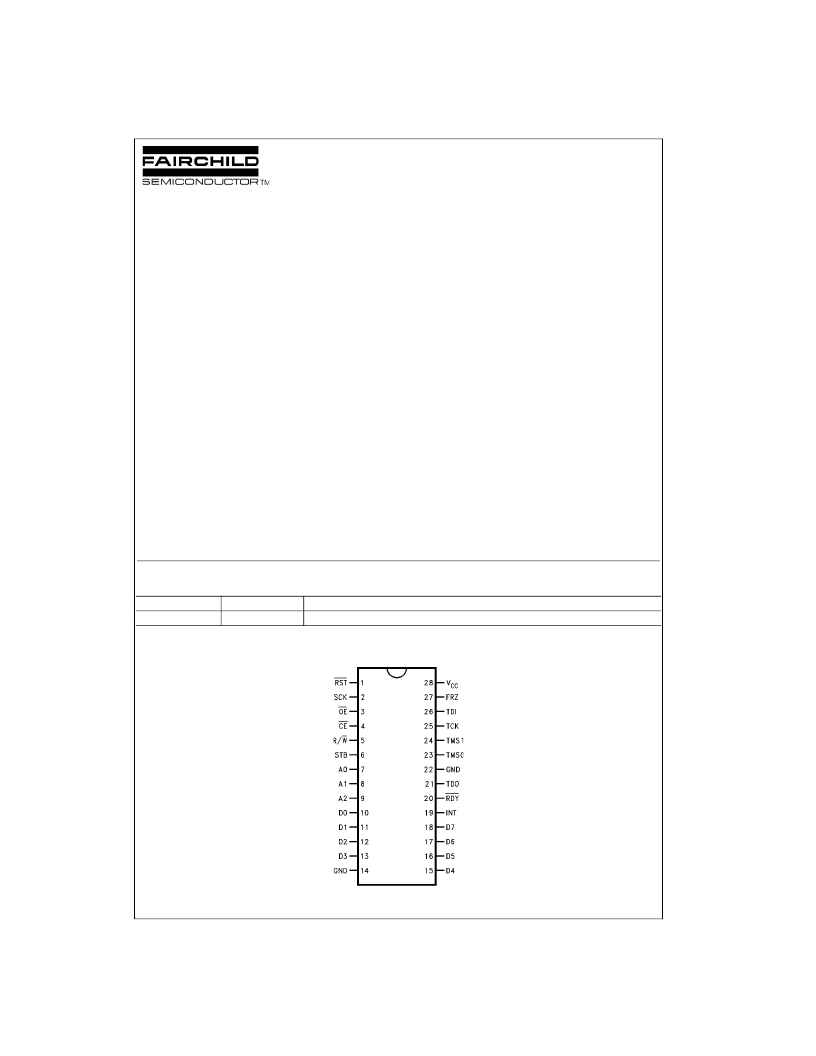

Connection Diagram

FACT

is a trademark of Fairchild Semiconductor Corporation.

Order Number

SCANPSC100FSC

Package Number

M28B

Package Description

28-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 Wide

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SCANPSC110FSC | SCAN Bridge Hierarchical and Multidrop Addressable JTAG Port (IEEE1149.1 System Test Support) |

| SCP-5453 | SOCKET,IC,16PIN,MACHINE TOOLED WIRE WRAP,0.3"WIDE,0.515"LEAD |

| SCP-6122 | POWER OPERATIONAL AMPLIFIER |

| SCS152 | HM Series Hermetically Sealed Basic Switch, Single Pole Double Throw Circuitry, 0.5 A at 28 Vdc, Integral Lever Actuator, Solder Termination |

| SCS152-IS | Small glass bead with axial leads |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SCANPSC100FSCX | 功能描述:接口 - 專用 Emb Boun Scan Cont RoHS:否 制造商:Texas Instruments 產(chǎn)品類型:1080p60 Image Sensor Receiver 工作電源電壓:1.8 V 電源電流:89 mA 最大功率耗散: 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:BGA-59 |

| SCANPSC110 | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:SCAN Bridge Hierarchical and Multidrop Addressable JTAG Port (IEEE1149.1 System Test Support) |

| SCANPSC110_ZFC3026B WAF | 制造商:Fairchild Semiconductor Corporation 功能描述: |

| SCANPSC110F | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:SCAN Bridge Hierarchical and Multidrop Addressable JTAG Port (IEEE1149.1 System Test Support) |

| SCANPSC110FDMQB | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:SCAN Bridge Hierarchical and Multidrop Addressable JTAG Port (IEEE1149.1 System Test Support) |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。