- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372063 > RJ80530VZ733256 Microprocessor PDF資料下載

參數(shù)資料

| 型號(hào): | RJ80530VZ733256 |

| 英文描述: | Microprocessor |

| 中文描述: | 微處理器 |

| 文件頁(yè)數(shù): | 17/89頁(yè) |

| 文件大小: | 1672K |

| 代理商: | RJ80530VZ733256 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)當(dāng)前第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)

Mobile Intel

Pentium

III Processor-M Datasheet

298340-002

Datasheet

17

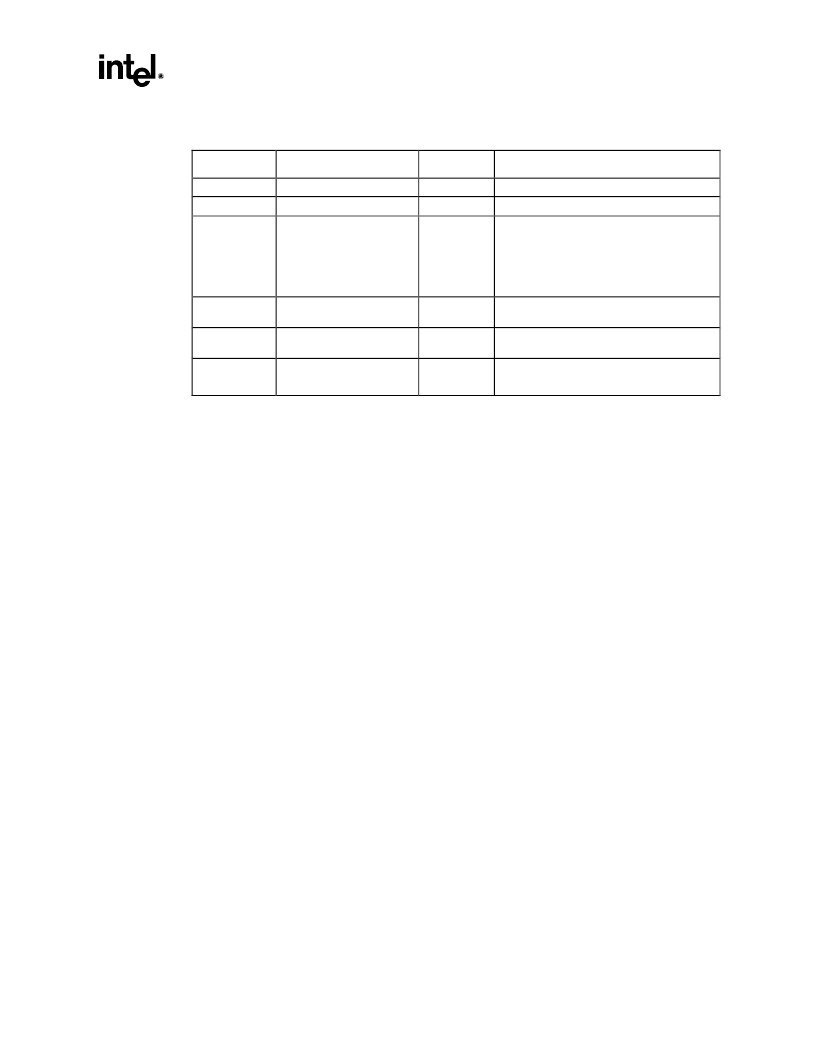

Table 2. Clock State Characteristics

Clock State

Exit Latency

Snooping

System Uses

Normal

N/A

Yes

Normal program execution

Auto Halt

10

μ

sec

Through snoop, to

HALT/Grant Snoop state:

immediate

Through STPCLK#, to

Normal state:

10 μ

sec

Yes

S/W controlled entry idle mode

Quick Start

Yes

H/W controlled entry/exit mobile throttling

HALT/Grant

Snoop

A few bus clocks after

snoop completion

Yes

Supports snooping in the low power states

Deep Sleep

30

μ

sec

No

H/W controlled entry/exit mobile powered-on

suspend support

Deeper Sleep

Platform Dependent

100

μ

sec (recommended)

No

H/W controlled entry/exit mobile powered-on

suspend support

2.2.8

Operating System Implications of Low-power States

The time-stamp counter and the performance monitor counters are not guaranteed to count in the

Quick Start state. The local APIC timer and performance monitor counter interrupts should be disabled

before entering the Deep Sleep state or the resulting behavior will be unpredictable.

2.2.9

Enhanced Intel SpeedStep Technology

The Mobile Intel Pentium

III

Processor-M supports Enhanced Intel SpeedStep technology. Enhanced

Intel SpeedStep technology allows the processor to switch between two core frequencies automatically

based on CPU demand, without having to reset the processor or change the system bus frequency. The

processor has two bus ratios programmed into it instead of one and the GHI# signal controls which one

is used. After reset, the processor will start in the lower of its two core frequencies, the “Battery

Optimized” mode. An operating mode transition to the high core frequency can be made by putting the

processor into the Deep Sleep state, raising the core voltage, setting GHI# low, and returning to the

Normal state. This puts the processor into the “Maximum performance” mode. Reversing these steps

transitions the processor back to the low-core frequency. Please contact your Intel Field Sales

Representative for details on how Enhanced Intel SpeedStep technology can be implemented with the

Mobile Intel Pentium

III

Processor-M, Intel 830MP chipset, or its equivalent.

2.3

AGTL Signals

The Mobile Pentium

III

Processor-M system bus signals use a variation of the low-voltage swing GTL

signaling technology. The AGTL system bus depends on incident wave switching and uses flight time

for timing calculations of the AGTL signals, as opposed to capacitive derating. Intel recommends

analog signal simulation of the system bus including trace lengths. Contact your field sales

representative to receive the IBIS models for the Mobile Pentium

III

Processor-M.

The AGTL system bus of the Mobile Pentium

III

Processor-M is designed to support high-speed data

transfers with multiple loads on a long bus that behaves like a transmission line. This termination is

provided on the processor core (except for the RESET# signal).

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RHFL4913 | THREE-TERMINAL POSITIVE FIXED VOLTAGE REGULATORS |

| RHFL4913S50-04V | THREE-TERMINAL POSITIVE FIXED VOLTAGE REGULATORS |

| RHFL4913ESY5005V | Converta Box Enclosure; Enclosure Material:Aluminum; External Height:2"; External Width:8"; External Depth:4"; Enclosure Color:Natural |

| RHFL4913ESY3305V | Standard Recovery Rectifier; Forward Current:20A; Forward Current Average:12.7A; Forward Current Avg Rectified, IF(AV):12.7A; Forward Surge Current Max, Ifsm:300A; Forward Voltage:1.1V; Forward Voltage Max, VF:1.1V RoHS Compliant: Yes |

| RHFL4913ESY3306V | Standard Recovery Rectifier; Forward Current:20A; Forward Current Average:12.7A; Forward Current Avg Rectified, IF(AV):12.7A; Forward Surge Current Max, Ifsm:300A; Forward Voltage:1.1V; Forward Voltage Max, VF:1.1V RoHS Compliant: Yes |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| RJ80530VZ800256 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| RJ80535GC0171M | 制造商:Rochester Electronics LLC 功能描述:MOBILE PENTIUM M,1.4GHZ,1M,UFCBGA - Bulk 制造商:Intel 功能描述: |

| RJ80535GC0171M S L6F5 | 制造商:Intel 功能描述:MPU Pentium? M Processor RISC 32-Bit 130nm 1.4GHz 479-Pin HPBGA Tray 制造商:Intel 功能描述:PENTIUM M PROCESSOR 1.40 GHZ |

| RJ80535GC0211M | 制造商:Intel 功能描述: |

| RJ80535GC0251M | 制造商:Rochester Electronics LLC 功能描述:MOBILE PENTIUM M,1.6GHZ,1M,UFCBGA - Bulk |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。