- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄367854 > PDI1394L11 (NXP Semiconductors N.V.) 1394 AV Link Layer Controller(AV(音頻/視頻)鏈接層控制器) PDF資料下載

參數(shù)資料

| 型號(hào): | PDI1394L11 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | 1394 AV Link Layer Controller(AV(音頻/視頻)鏈接層控制器) |

| 中文描述: | 1394影音鏈路層控制器(視聽(tīng)(音頻/視頻)鏈接層控制器) |

| 文件頁(yè)數(shù): | 11/46頁(yè) |

| 文件大?。?/td> | 294K |

| 代理商: | PDI1394L11 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)當(dāng)前第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)

Philips Semiconductors

Product specification

PDI1394L11

1394 AV link layer controller

1997 Oct 21

11

SV00686

T

AS

HIF CS_N

HIF RD_N

HIF WR_N

HIF A0..HIF A7

HIF D0..HIF D7

T

AS

T

ACC

T

ACC

RSR

O

RSR

n

RSR

n

HIF A8

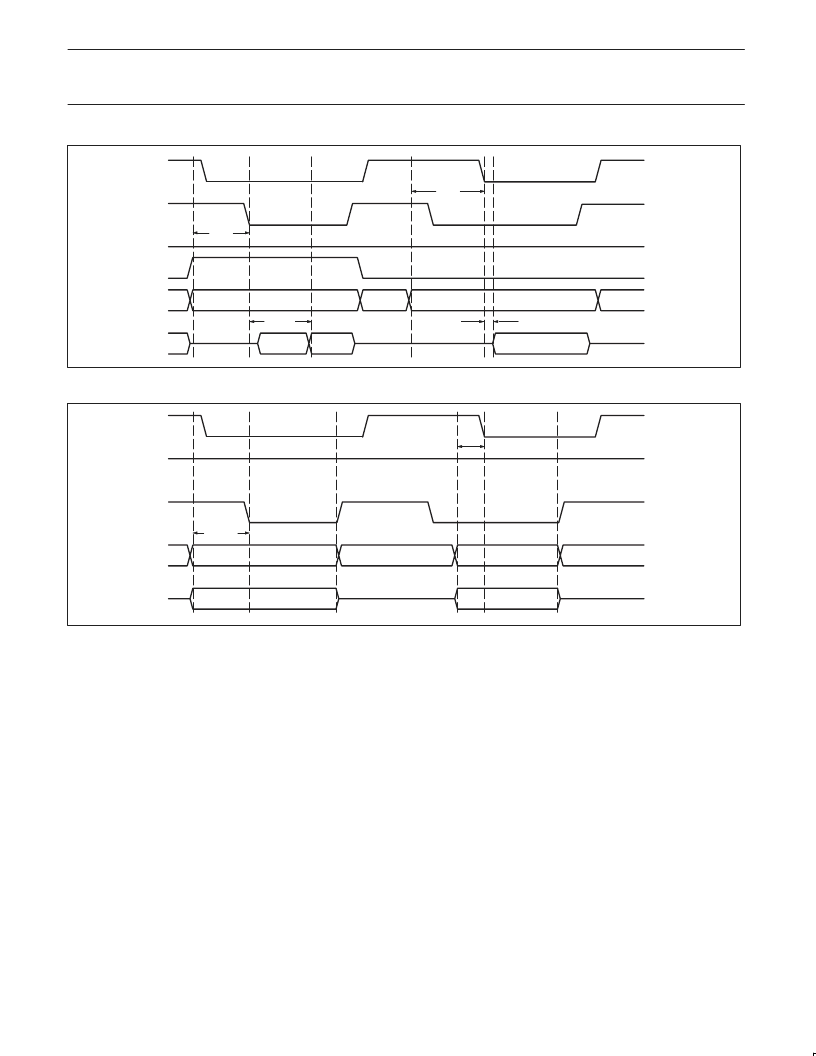

Figure 2. Read cycle signal timing (2 independent read cycles)

SV00687

T

AS

HIF CS_N

HIF RD_N

HIF WR_N

HIF A0..HIF A8

HIF D0..HIF D7

T

AS

<WRITE DATA>

<WRITE DATA>

<VALID ADDRESS>

<VALID ADDRESS>

Figure 3. Write cycle signal timing (2 independent write cycles)

12.4

The PDI1394L11 provides an interface to asynchronous data

packets through the registers in the host interface. The format of the

asynchronous packets is specified in the following sections.

The Asynchronous Packet Interface

12.4.1

Upon reception of a packet, the packet data is stored in the

appropriate receive FIFO, either the Request or Response FIFO.

The location of the packet is indicated by either the RREQQQAV or

RRSPQAV status bit being set in the Asynchronous Interrupt

Acknowledge (ASYINTACK) register. The packet is transferred out

of the FIFO by successive reads of the Asynchronous Receive

Request (RREQ) or Asynchronous Receive Response (RRSP)

register. The end of the packet (the last quadlet) is indicated by

either the RREQQLASTQ or RRSPQLASTQ bit set in ASYINTACK.

Attempting to read the FIFO when either RREQQQAV bit or

RRSPQQAV bit is set to 0 (in the Asynchronous RX/TX interrupt

acknowledge (ASYINTACK) register) will result in a queue read

error.

Reading an Asynchronous Packet

12.4.2

An asynchronous packet intended for transmission is first stored in

the appropriate Transmitter FIFO. Once writing to the FIFO is

complete, the link layer controller arbitrates for the bus to transmit

the packet.

Writing an Asynchronous Packet

To generate an asynchronous packet, the first and next to last

quadlets of the packet must be written to the Asynchronous

Transmit Request Next (TX_RQ_NEXT) register, for request type

packets, or the Asynchronous Transmit Response Next

(TX_RP_NEXT) register, for response type packets. The last

quadlet of the packet is written to the Asynchronous Transmit

Request Last (TX_RQ_LAST) register, for request type packets, or

the Asynchronous Transmit Response Last (TX_RP_LAST)

register, for response type packets. After writing the last quadlet,

the packet is automatically queued by the AVlink layer controller for

transmission over the bus.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PDI1394L21 | Full Duplex AV Link Layer Ccontroller(全雙工AV鏈接層控制器) |

| PDI1394L41 | Content Protection AV Link Layer(內(nèi)容可保護(hù)的AV鏈接層控制器) |

| PDI1394P21 | 3-port Physical Layer Interface(三端口物理層接口) |

| PDI1394P22 | 3-port Physical Layer Interface(三端口物理層接口) |

| PDI1394P24 | 2-port 400 Mbps physical layer interface(2端口 400 Mbps物理層接口) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PDI1394L11BA | 制造商:PHILIPS 制造商全稱(chēng):NXP Semiconductors 功能描述:1394 AV link layer controller |

| PDI1394L11BA-S | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:IEEE 1394 (Firewire) Bus Interface/Controller |

| PDI1394L21 | 制造商:PHILIPS 制造商全稱(chēng):NXP Semiconductors 功能描述:1394 full duplex AV link layer controller |

| PDI1394L21BE | 制造商:PHILIPS 制造商全稱(chēng):NXP Semiconductors 功能描述:1394 full duplex AV link layer controller |

| PDI1394L21BP | 制造商:PHILIPS 制造商全稱(chēng):NXP Semiconductors 功能描述:1394 full duplex AV link layer controller |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。