- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄180051 > M-ORT82G52BM680-DB (LATTICE SEMICONDUCTOR CORP) FPGA, 1296 CLBS, 333000 GATES, PBGA680 PDF資料下載

參數(shù)資料

| 型號: | M-ORT82G52BM680-DB |

| 廠商: | LATTICE SEMICONDUCTOR CORP |

| 元件分類: | FPGA |

| 英文描述: | FPGA, 1296 CLBS, 333000 GATES, PBGA680 |

| 封裝: | PLASTIC, FBGA-680 |

| 文件頁數(shù): | 15/94頁 |

| 文件大小: | 2104K |

| 代理商: | M-ORT82G52BM680-DB |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁當前第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁

Lattice Semiconductor

ORCA ORT82G5 Data Sheet

22

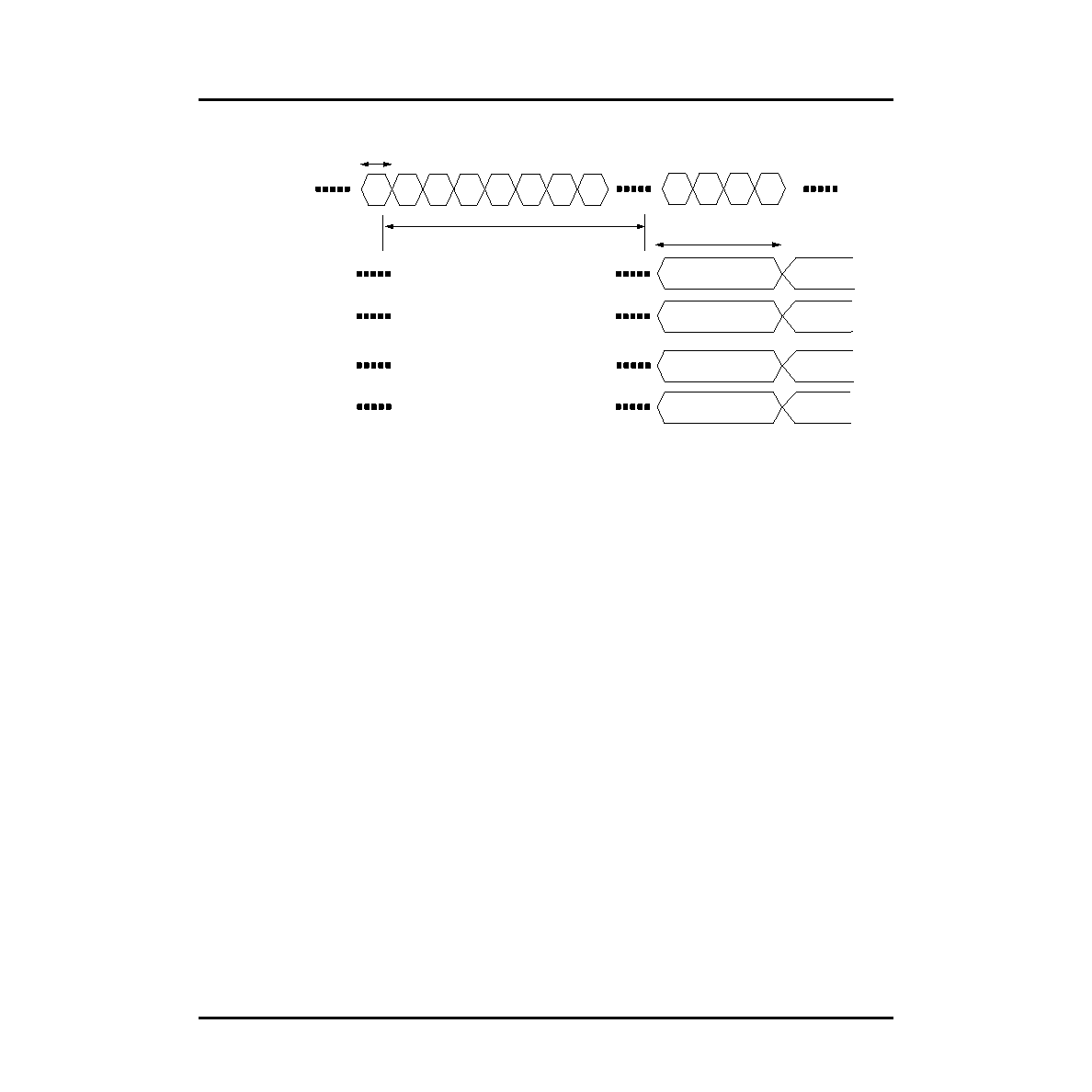

Figure 8. Receive DEMUX Block for a Single SERDES Channel

One clock per bank of 4 channels called RCK78[A,B] is sent to the FPGA. The control bits RCKSEL[A,B] are used

to select the channel that is the source for these clocks.

Link State Machines

Two link state machines are included in the ORT82G5, one for XAUI applications and a second for Fibre Channel

applications.

The Fibre Channel link state machine is responsible for establishing a valid link between the transmitter and the

receiver and for maintaining link synchronization. The machine is initially in the Loss Of Synchronization (LOS)

state upon power-on reset. This is indicated by WDSYNC_xx = 0. While in this state, the machine looks for a partic-

ular number of consecutive idle ordered sets without any invalid data transmission in between before declaring syn-

chronization achieved. Achievement of synchronization is indicated by asserting WDSYNC_xx = 1. Specically, the

machine looks for three continuous idle ordered sets without any misaligned comma character or any running dis-

parity based code violation in between. In the event of any such code violation, the machine would reset itself to the

ground state and start its search for the idle ordered sets again. A typical valid sequence for achieving link synchro-

nization would be K28.5 D21.4 D21.5 D21.5 repeated 3 times.

In the synchronization achieved state, the machine constantly monitors the received data and looks for any kind of

code violation that might result due to running disparity errors. If it were to receive four such consecutive invalid

words, the link machine loses its synchronization and once again enters the loss of synchronization state (LOS). A

pair of valid words received by the machine overcomes the effect of a previously encountered code violation. LOS

is indicated by the status of WDSYNC_xx output which now transitions from 1 to 0. At this point the machine

attempts to establish the link yet again. Figure 9 shows the state diagram for the Fibre Channel link state machine.

In the ORT82G5 LOS is also indicated by DEMUXWAS_xx status register bit. This bit is set to 0 during loss of syn-

chronization.

pq

r

s

t

x

y

z

SRBDxx[9:0]

10-bit

p

7-0

40-bit

RWD_xx[31:24]

RWD_xx[23:16]

RWD_xx[15:8]

RWD_xx[7:0]

LATENCY = 4 RSYS_CLK [A1,...,B2] CLOCKS

p

8

p

9

t

7-0

t

8

t

9

q

7-0

q

8

q

9

x

7-0

x

8

x

9

r

7-0

r

8

r

9

y

7-0

y

8

y

9

s

7-0

s

8

s

9

z

7-0

z

8

z

9

RWBIT8_xx[3]

RWBIT9_xx[3]

RWBIT8_xx[2]

RWBIT8_xx[1]

RWBIT8_xx[0]

RWBIT9_xx[2]

RWBIT9_xx[1]

RWBIT9_xx[0]

相關PDF資料 |

PDF描述 |

|---|---|

| M.PI-1R1D12 | 1 ELEMENT, 1.1 uH, GENERAL PURPOSE INDUCTOR, SMD |

| M01-014-1452PA | 14 CONTACT(S), MALE, RIGHT ANGLE TELECOM AND DATACOM CONNECTOR, SOLDER |

| M01-016-1443PA | 16 CONTACT(S), MALE, RIGHT ANGLE TELECOM AND DATACOM CONNECTOR, SOLDER |

| M0302CS-9N2XJSU | 1 ELEMENT, 0.0092 uH, CERAMIC-CORE, GENERAL PURPOSE INDUCTOR, SMD |

| M0302CS-7N4XJSW | 1 ELEMENT, 0.0074 uH, CERAMIC-CORE, GENERAL PURPOSE INDUCTOR, SMD |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| MORTAR-44LB | 制造商:3M Electronic Products Division 功能描述:3M(TM) FIRE BARRIER MORTAR, 44 98040056073 制造商:3M Electronic Products Division 功能描述:Fire Barrier 44 lb Bag |

| MO-RX3930 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:FSK RECEIVER MODULE |

| MO-RX3930-FS | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:FSK RECEIVER MODULE |

| MO-RX3930-FS315M | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:FSK RECEIVER MODULE |

| MO-RX3930-FS434M | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:FSK RECEIVER MODULE |

發(fā)布緊急采購,3分鐘左右您將得到回復。