- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄385472 > LH79524N0F100A1 (NXP Semiconductors N.V.) System-on-Chip PDF資料下載

參數(shù)資料

| 型號(hào): | LH79524N0F100A1 |

| 廠商: | NXP Semiconductors N.V. |

| 元件分類(lèi): | 數(shù)學(xué)處理器 |

| 英文描述: | System-on-Chip |

| 封裝: | LH79524N0F100A1<SOT1019-1 (LFBGA208)|<<http://www.nxp.com/packages/SOT1019-1.html<1<Always Pb-free,;LH79525N0Q100A1<SOT1017-1 (LQFP176)|<<http://www.nxp.com/packages/SOT1 |

| 文件頁(yè)數(shù): | 23/64頁(yè) |

| 文件大小: | 970K |

| 代理商: | LH79524N0F100A1 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)當(dāng)前第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)

System-on-Chip

LH79524/LH79525

Preliminary data sheet

Rev. 01

—

16 July 2007

23

NXP Semiconductors

Universal Asynchronous Receiver

Transmitter (UART)

The LH79524/LH79525 incorporates three UARTs.

UART0, UART1, and UART2 offer similar functionality

to the industry-standard 16C550. They perform serial-

to-parallel conversion on data received from a periph-

eral device and parallel-to-serial conversion on data

transmitted to the UART. The CPU reads and writes

data and control status information through the AMBA

APB interface. The transmit and receive paths are buff-

ered with internal FIFO memories that support pro-

grammable-service 'trigger levels', and overrun

protection. These FIFO memories enable up to 32

characters to be stored independently in both transmit

and receive modes.

Programmable bits-per-character (5, 6, 7, or 8)

Optional nine-bit mode to tag and recognize

characters as either data or address

Nine-bit Transmit FIFO and 12-bit Receive FIFO

Programmable FIFO trigger points

DMA support for UART0

Programmable IrDA SIR input/output for each UART

Separate 16-byte transmit and receive FIFOs to

reduce CPU interrupts

Programmable FIFO disabling for 1-byte depth

Programmable baud rate generator

Independent masking of transmit FIFO, receive

FIFO, receive timeout and modem status interrupts

False start bit detection

Line break generation and detection

Fully-programmable serial interface characteristics:

– 5-, 6-, 7-, or 8-bit data word length

– Even-, odd-, or no-parity bit generation and

detection

– 1 or 2 stop bit generation

IrDA SIR Encode/Decode block, providing:

– Programmable use of IrDA SIR or UART input/

output

– Supports data rates up to 115.2 kbit/s half-duplex

– Programmable internal clock generator, allowing

division of the Reference clock in increments of 1

to 512 for low-power mode bit durations.

– Loopback for testing

Vectored Interrupt Controller (VIC)

The Vectored Interrupt Controller combines the

interrupt request signals from 20 internal and eight

external interrupt sources and applies them, after

masking and prioritization, to the IRQ and FIQ interrupt

inputs of the ARM7TDMI processor core.

The Interrupt Controller incorporates a hardware

interrupt vector logic with programmable priority for up

to 16 interrupt sources. This logic reduces the interrupt

response time for IRQ type interrupts compared to

solutions using software polling to determine the high-

est priority interrupt source. This significantly improves

the real-time capabilities of the LH79524/LH79525 in

embedded control applications.

20 internal and eight external interrupt sources

– Individually maskable

– Status accessible for software polling

IRQ interrupt vector logic for up to 16 channels with

programmable priorities

All of the interrupt channels, with the exception of the

Watchdog Timer interrupt, can be programmed to

generate:

– FIQ interrupt request

– Non-vectored IRQ interrupt request (software to

poll IRQ source)

– Vectored IRQ interrupt request (up to 16 chan-

nels total)

The Watchdog timer can only generate FIQ interrupt

requests

External interrupt inputs programmable

– Edge triggered or level triggered

– Rising edge/active HIGH or falling edge/active

LOW

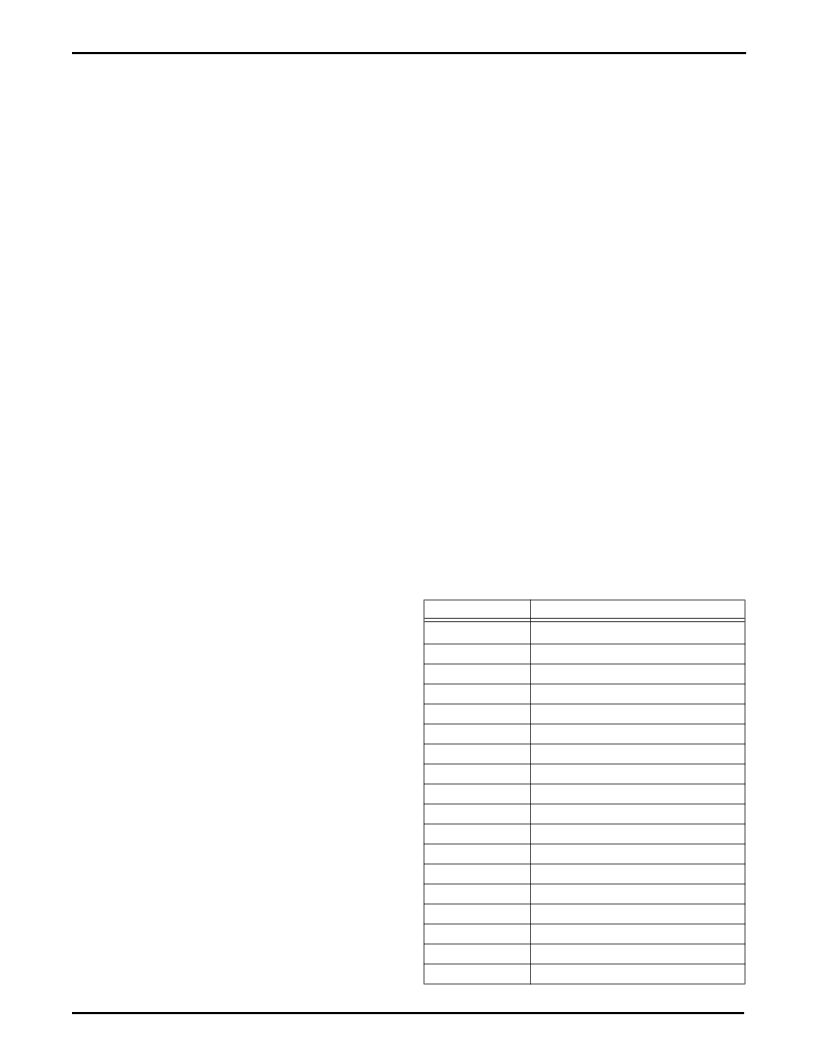

The 32 interrupt channels are shown in Table 10.

Table 10. Interrupt Channels

CHANNEL

INTERRUPT SOURCE

0

WDT

1

Not Used

2

COMRX (used for debug)

3

COMTX (used for debug)

4

Counter/Timer0 Combined

5

Counter/Timer1 Combined

6

Counter/Timer2 Combined

7

External Interrupt 0

8

External Interrupt 1

9

External Interrupt 2

10

External Interrupt 3

11

External Interrupt 4

12

External Interrupt 5

13

External Interrupt 6

14

External Interrupt 7

15

RTC_ALARM

16

ACD TSIRQ Combined

17

ADC Brown Out INTR

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LH79525N0Q100A1 | System-on-Chip |

| LH7A400N0F000B5 | 32-Bit System-on-Chip |

| LH7A400N0F076B5 | 32-Bit System-on-Chip |

| LH7A400N0G000B5 | 32-Bit System-on-Chip |

| LH7A404N0F000B3 | 32-Bit System-on-Chip |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LH79524N0F100A1,55 | 功能描述:ARM微控制器 - MCU LCD,USB,ETH’NET,MMU,ADC,BGA208 RoHS:否 制造商:STMicroelectronics 核心:ARM Cortex M4F 處理器系列:STM32F373xx 數(shù)據(jù)總線(xiàn)寬度:32 bit 最大時(shí)鐘頻率:72 MHz 程序存儲(chǔ)器大小:256 KB 數(shù)據(jù) RAM 大小:32 KB 片上 ADC:Yes 工作電源電壓:1.65 V to 3.6 V, 2 V to 3.6 V, 2.2 V to 3.6 V 工作溫度范圍:- 40 C to + 85 C 封裝 / 箱體:LQFP-48 安裝風(fēng)格:SMD/SMT |

| LH79524N0F100A1,551 | 制造商:NXP Semiconductors 功能描述: |

| LH79524N0F100A1;55 | 功能描述:ARM微控制器 - MCU LCD USB ETH’NET MMU RoHS:否 制造商:STMicroelectronics 核心:ARM Cortex M4F 處理器系列:STM32F373xx 數(shù)據(jù)總線(xiàn)寬度:32 bit 最大時(shí)鐘頻率:72 MHz 程序存儲(chǔ)器大小:256 KB 數(shù)據(jù) RAM 大小:32 KB 片上 ADC:Yes 工作電源電壓:1.65 V to 3.6 V, 2 V to 3.6 V, 2.2 V to 3.6 V 工作溫度范圍:- 40 C to + 85 C 封裝 / 箱體:LQFP-48 安裝風(fēng)格:SMD/SMT |

| LH79524N0F100A1-S | 功能描述:ARM微控制器 - MCU ARM7 LCD MMU ENET RoHS:否 制造商:STMicroelectronics 核心:ARM Cortex M4F 處理器系列:STM32F373xx 數(shù)據(jù)總線(xiàn)寬度:32 bit 最大時(shí)鐘頻率:72 MHz 程序存儲(chǔ)器大小:256 KB 數(shù)據(jù) RAM 大小:32 KB 片上 ADC:Yes 工作電源電壓:1.65 V to 3.6 V, 2 V to 3.6 V, 2.2 V to 3.6 V 工作溫度范圍:- 40 C to + 85 C 封裝 / 箱體:LQFP-48 安裝風(fēng)格:SMD/SMT |

| LH79525 | 制造商:PHILIPS 制造商全稱(chēng):NXP Semiconductors 功能描述:System-on-Chip |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。