- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384480 > ID82C284 (Intersil Corporation) Clock Generator and Ready Interface for 80C286 Processors PDF資料下載

參數(shù)資料

| 型號: | ID82C284 |

| 廠商: | Intersil Corporation |

| 英文描述: | Clock Generator and Ready Interface for 80C286 Processors |

| 中文描述: | 時鐘發(fā)生器和Ready接口80C286處理器 |

| 文件頁數(shù): | 4/11頁 |

| 文件大?。?/td> | 72K |

| 代理商: | ID82C284 |

4

The 82C284 provides a second clock output, PCLK, for periph-

eral devices. PCLK is CLK divided by two. PCLK has a duty

cycle of 50% and CMOS output drive characteristics. PCLK is

normally synchronized to the internal processor clock.

After reset, the PCLK signal may be out of phase with the inter-

nal processor clock. The S1 and S0 signals of the first bus

cycle are used to synchronize PCLK to the internal processor

clock. The phase of the PCLK output changes by extending its

HIGH time beyond one system clock (see waveforms). PCLK is

forced HIGH whenever either S0 or S1 were active (LOW) for

the two previous CLK cycles. PCLK continues to oscillate when

both S0 and S1 are HIGH.

Since the phase of the internal processor clock will not change

except during reset, the phase of PCLK will not change except

during the first bus cycle after reset.

Oscillator

The oscillator circuit of the 82C284 is a linear Pierce oscillator

which requires an external parallel resonant, fundamental

mode, crystal. The output of the oscillator is internally buffered.

The crystal frequency chosen should be twice the required

internal processor clock frequency. The crystal should have a

typical load capacitance of 32pF.

X1 and X2 are the oscillator crystal connections. For stable

operation of the oscillator, two loading capacitors are recom-

mended, as shown in Table 1. The sum of the board capaci-

tance and loading capacitance should equal the values shown.

It is advisable to limit stray board capacitances (not including

the effect of the loading capacitors or crystal capacitance) to

less than 10pF between the X1 and X2 pins. Decouple V

CC

and GND as close to the 82C284 as possible with a 0.1

μ

F poly-

carbonate capacitor.

CLK Termination

Due to the CLK output having a very fast rise and fall time, it is

recommended to properly terminate the CLK line at frequen-

cies above 10MHz to avoid signal reflections and ringing. Ter-

mination is accomplished by inserting a small resistor

(typically 10-74

) in series with the output, as shown in Figure

2. This is known as series termination. The resistor value plus

the circuit output impedance (approximately 25

) should be

made equal to the impedance of the transmission line.

Reset Operation

The reset logic provides the RESET output to force the sys-

tem into a known, initial state. When the RES input is active

(LOW), the RESET output becomes active (HIGH), RES is

synchronized internally at the falling edge of CLK before

generating the RESET output (see waveforms). Synchroni-

zation of the RES input introduces a one or two CLK delay

before affecting the RESET Output.

At power up, a system does not have a stable V

CC

and CLK.

To prevent spurious activity, RES should be asserted until

V

CC

and CLK stabilize at their operating values. 80C286

processors and support components also require their

RESET inputs be HIGH a minimum of 16 CLK cycles. An RC

network, as shown in Figure 3, will keep RES LOW long

enough to satisfy both needs.

A Schmitt trigger input with hysteresis on RES assures a single

transition of RESET with an RC circuit on RES. The hysteresis

separates the input voltage level at which the circuit output

switches from HIGH to LOW from the input voltage level at

which the circuit output switches from LOW to HIGH. The RES

HIGH to LOW input transition voltage is lower than the RES

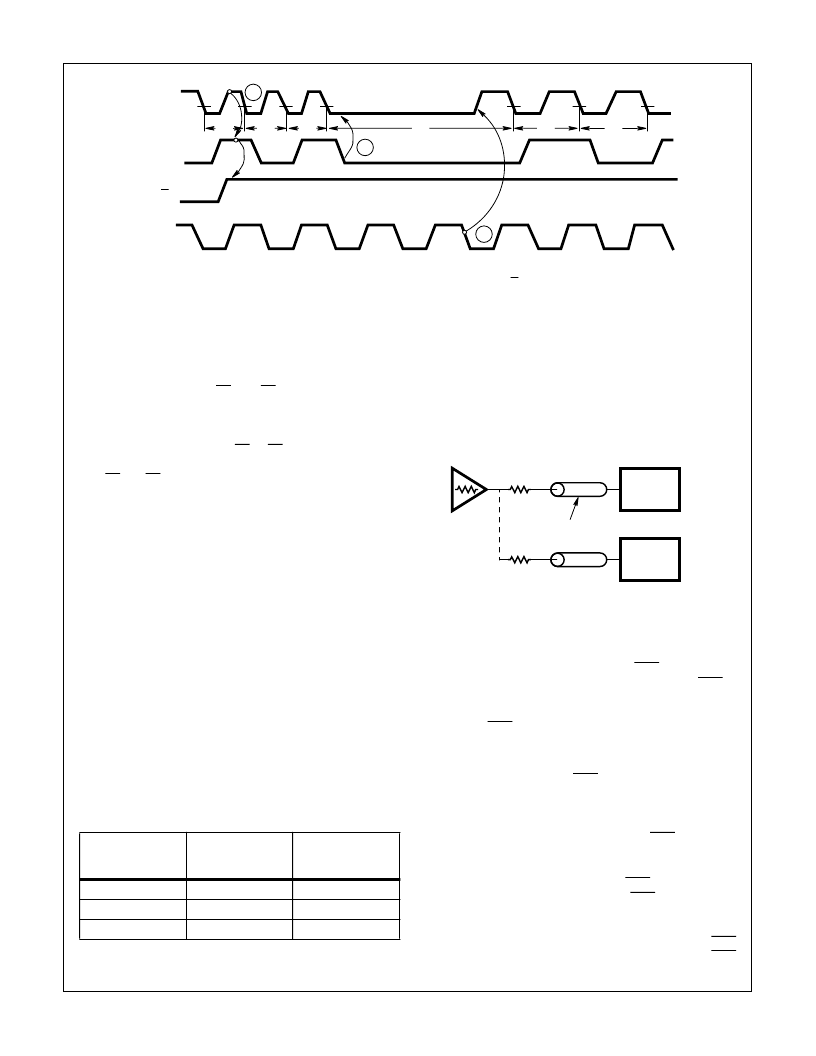

FIGURE 1B. F/C SWITCHED FROM LOW (USING THE CRYSTAL INPUT X1) TO HIGH (USING THE EFI INPUT)

FIGURE 1. DYNAMICALLY SWITCHING THE F/C PIN

CLK

PCLK

F/C

EFI

1

φ

2

φ

1

φ

2

φ

1

φ

2

2

3

φ

1

TABLE 1. 82C284 CRYSTAL LOADING CAPACITANCE VALUES

CRYSTAL

FREQUENCY

Cl

CAPACITANCE

(PIN 7)

C2

CAPACITANCE

(PIN 8)

1MHz to 8MHz

60pF

40pF

8MHz to 20MHz

25pF

15pF

20MHz to 25MHz

15pF

15pF

CLK

OUT

CLOSELY

PLACED

LOADS

CLOSELY

PLACED

LOADS

R

TRANSMISSION

LINE

RO

≈

25

FIGURE 2. SERIES TERMINATION

Z

Z

82C284

相關PDF資料 |

PDF描述 |

|---|---|

| ID82C82 | CMOS Octal Latching Bus Driver |

| ID82C83H | CMOS Octal Latching Inverting Bus Driver |

| ID82C84A | RES,CHIP 1/8W 5% 33 OHM |

| ID82C85 | CMOS Static Clock Controller/Generator |

| ID82C86H | CMOS Octal Bus Transceiver |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| ID82C284-10 | 制造商:Harris Corporation 功能描述: 制造商:Intersil Corporation 功能描述: |

| ID82C284-12 | 制造商:Rochester Electronics LLC 功能描述:PERIPH CLK GENERATOR 5V 12.5MHZ 18CDIP IND - Bulk |

| ID82C37A | 制造商:HARRIS 制造商全稱:HARRIS 功能描述:CMOS High Performance Programmable DMA Controller |

| ID82C37A-12 | 制造商:HARRIS 制造商全稱:HARRIS 功能描述:CMOS High Performance Programmable DMA Controller |

| ID82C37A-5 | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Harris Corporation 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復。