- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384480 > ID82C284 (Intersil Corporation) Clock Generator and Ready Interface for 80C286 Processors PDF資料下載

參數(shù)資料

| 型號(hào): | ID82C284 |

| 廠商: | Intersil Corporation |

| 英文描述: | Clock Generator and Ready Interface for 80C286 Processors |

| 中文描述: | 時(shí)鐘發(fā)生器和Ready接口80C286處理器 |

| 文件頁(yè)數(shù): | 3/11頁(yè) |

| 文件大?。?/td> | 72K |

| 代理商: | ID82C284 |

3

Functional Description

Introduction

The 82C284 generates the clock, ready, and reset signals

required for 80C286 processors and support components.

The 82C284 is packaged in an 18-pin DIP and contains a

crystal controlled oscillator, clock generator, peripheral clock

generator, MULTIBUS ready synchronization logic, and

system reset generation logic.

Clock Generator

The CLK output provides the basic timing control for an

80C286 system. CLK has output characteristics sufficient to

drive CMOS devices. CLK is generated by either an internal

crystal oscillator, or an external source as selected by the

F/C input pin. When F/C is LOW, the crystal oscillator drives

the CLK output. When F/C is HIGH, the EFI input drives the

CLK output.

The F/C pin on the Intersil 82C284 is dynamically switch-

able. This allows the CLK frequency to the processor to be

changed from one frequency to another in a running system.

With this feature, a system can be designed which operates

at maximum speed when needed, and then dynamically

switched to a lower frequency to implement a low-power

mode. The lower frequency can be anything down to, but

excluding, DC. The following 3 conditions apply when

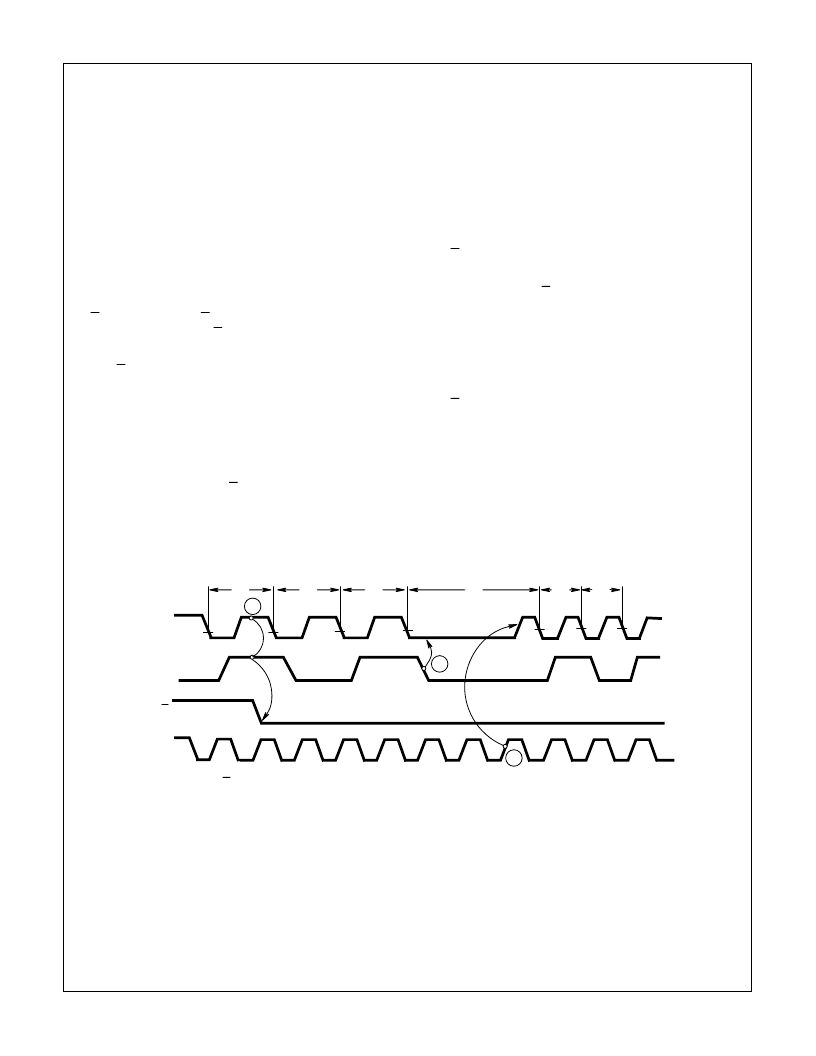

dynamically switching the F/C pin (see Figure 1):

1)

The CLK is stretched in the low portion of the

φ

2 phase

of its cycle during transition from one CLK frequency to

the other (see Waveforms).

2)

When switching CLK frequency sources, there is a max-

imum transition latency of 2.5 clock cycles of the fre-

quency being switched to, from the time CLK freezes

low, until CLK restarts at the new frequency (see Wave-

forms).

3)

The maximum latency from the time F/C is dynamically

switched, to the time CLK freezes low, is 4 CLK cycles

(see Waveforms).

The following steps describe the sequence of events that

transpire when F/C is dynamically switched:

A)

F/C switched from high (using EFI input) to low (using

the crystal input X1 - see Figure 1A).

1) The state of F/C is sampled when both CLK and

PCLK are high until a change is detected.

2) On the second following falling edge of PCLK, CLK is

frozen low.

3) CLK restarts at the crystal frequency on the rising

edge of Xl, after the second falling edge of X1.

B)

F/C switched from low (using the crystal input Xl) to high

(using the EFI input - see Figure 1B).

1) The state of F/C is sampled when both CLK and

PCLK are high until a change is detected.

2) On the second following falling edge of PCLK, CLK is

frozen low.

3) CLK restarts at the EFI input frequency on the falling

edge of EFl after the second rising edge of EFI.

FIGURE 1A. F/C SWITCHED FROM HIGH (USING EFI INPUT) TO LOW (USING THE CRYSTAL INPUT X1)

φ

2

φ

1

φ

2

φ

1

φ

2

φ

1

1

2

3

CLK

PCLK

F/C

X1

82C284

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ID82C82 | CMOS Octal Latching Bus Driver |

| ID82C83H | CMOS Octal Latching Inverting Bus Driver |

| ID82C84A | RES,CHIP 1/8W 5% 33 OHM |

| ID82C85 | CMOS Static Clock Controller/Generator |

| ID82C86H | CMOS Octal Bus Transceiver |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ID82C284-10 | 制造商:Harris Corporation 功能描述: 制造商:Intersil Corporation 功能描述: |

| ID82C284-12 | 制造商:Rochester Electronics LLC 功能描述:PERIPH CLK GENERATOR 5V 12.5MHZ 18CDIP IND - Bulk |

| ID82C37A | 制造商:HARRIS 制造商全稱:HARRIS 功能描述:CMOS High Performance Programmable DMA Controller |

| ID82C37A-12 | 制造商:HARRIS 制造商全稱:HARRIS 功能描述:CMOS High Performance Programmable DMA Controller |

| ID82C37A-5 | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Harris Corporation 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。