- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1909 > CS8952-IQZ (Cirrus Logic Inc)IC TXRX 100/10 PHY 100TQFP PDF資料下載

參數(shù)資料

| 型號: | CS8952-IQZ |

| 廠商: | Cirrus Logic Inc |

| 文件頁數(shù): | 58/81頁 |

| 文件大小: | 0K |

| 描述: | IC TXRX 100/10 PHY 100TQFP |

| 標(biāo)準(zhǔn)包裝: | 90 |

| 類型: | 收發(fā)器 |

| 規(guī)程: | MII |

| 電源電壓: | 4.75 V ~ 5.25 V |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 100-LQFP |

| 供應(yīng)商設(shè)備封裝: | 100-TQFP(14x14) |

| 包裝: | 托盤 |

| 產(chǎn)品目錄頁面: | 759 (CN2011-ZH PDF) |

| 其它名稱: | 598-1208 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁當(dāng)前第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁

CS8952

CrystalLAN 100BASE-X and 10BASE-T Transceiver

61

DS206F1

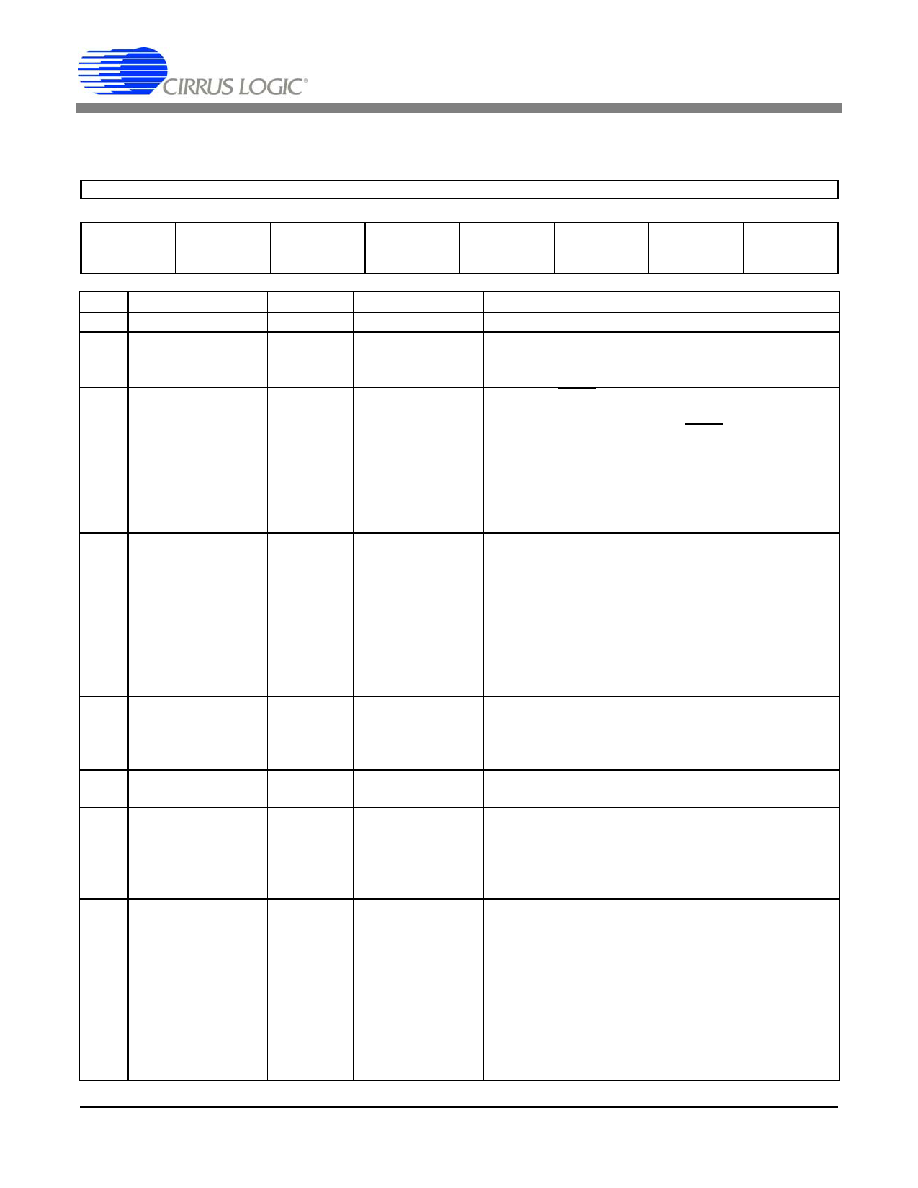

6.20

10BASE-T Configuration Register - Address 1Ch

15

14

13

12

11

10

9

8

Reserved

7

654

32

10

National

Compatibility

Mode

LED3 Blink

Enable

Enable LT/10

SQE Enable

Reserved

Low Rx

Squelch

Polarity

Disable

Jabber Enable

BIT

NAME

TYPE

RESET

DESCRIPTION

15:8

Reserved

Read Only

0000 0000

7

National Compati-

bility Mode

Read/Write 1

When set, registers and bits that are not compatible

with the National DP83840 are disabled and writes to

these registers are ignored.

6

LED3 Blink Enable

Read/Write 0

When set, LED3 will blink during auto-negotiation

and will indicate Link Good status upon completion of

auto-negotiation. When clear, LED3 indicates Link

Good status only.

Note: This bit is disabled, and writes to this bit are

ignored when the National Compatibility Mode bit (bit

7) is set.

5

Enable LT/10

Read/Write 1

When set, this bit enables the transmission of link

pulses.

When clear, link pulses are disabled and a good link

condition is forced. If link pulses are disabled during

100 Mb/s operation with auto-negotiation enabled,

the CS8952 will go into 10 Mb/s mode. If operating in

100 Mb/s mode with no auto-negotiation, then clear-

ing this bit has no effect.

4

SQE Enable

Read/Write Reset to the logic

inverse of the

value on the

REPEATER pin.

When set, and if the CS8952 is in half-duplex mode,

this bit enables the 10BASE-T SQE function. When

the part is in repeater mode, this bit is cleared and

may not be set.

3

Reserved

Read Only

1

This bit should be read as a don’t care and, when

written, should be written to 1.

2

Low Rx Squelch

Read/Write 0

When clear, the 10BASE-T receiver squelch thresh-

olds are set to levels defined by the ISO/IEC 8802-3

specification. When set, the thresholds are reduced

by approximately 6 dB. This is useful for operating

with “quiet” cables that are longer than 100 meters.

1

Polarity Disable

Read/Write 0

The 10BASE-T receiver automatically determines

the polarity of the received signal at the RXD+/RXD-

input. When this bit is clear, the polarity is corrected,

if necessary. When set, no effort is made to correct

the polarity. Polarity correction will only be performed

during 10BASE-T packet reception.

Note: This bit is disabled, and writes to this bit are

ignored when the National Compatibility Mode bit (bit

7) is set.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY8CLED04DOCD1-56LTXI | IC POWERPSOC DEBUG 4CH 1A 56VQFN |

| CYG2217 | IC MOD PHONE LINE WIRE 1.07" PCB |

| DAC312ER | IC DAC 12BIT MULT HS 20-CDIP |

| DAC8143FPZ | IC DAC 12BIT DAISYCHAIN 16DIP |

| DAC8228FSZ | IC DAC 8BIT DUAL V-OUT 20SOIC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CS8952-IQZR | 功能描述:以太網(wǎng) IC IC 100BASE-TX and 10BASE-T Transceiver RoHS:否 制造商:Micrel 產(chǎn)品:Ethernet Switches 收發(fā)器數(shù)量:2 數(shù)據(jù)速率:10 Mb/s, 100 Mb/s 電源電壓-最大:1.25 V, 3.45 V 電源電壓-最小:1.15 V, 3.15 V 最大工作溫度:+ 85 C 封裝 / 箱體:QFN-64 封裝:Tray |

| CS8952T | 制造商:CIRRUS 制造商全稱:Cirrus Logic 功能描述:100BASE E-X AND 10BASE-T TRANSCEIVER |

| CS8952T-CQ | 制造商:CIRRUS 制造商全稱:Cirrus Logic 功能描述:100BASE E-X AND 10BASE-T TRANSCEIVER |

| CS8952T-IQ | 制造商:CIRRUS 制造商全稱:Cirrus Logic 功能描述:100BASE E-X AND 10BASE-T TRANSCEIVER |

| CS8952T-IQR | 制造商:Cirrus Logic 功能描述:ETHERNET TXRX SGL CHIP 1-PORT 5V 10MBPS/100MBPS 100TQFP - Tape and Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。