- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1909 > CS61584A-IQ3Z (Cirrus Logic Inc)IC LINE INTERFACE T1/E1 64LQFP PDF資料下載

參數(shù)資料

| 型號: | CS61584A-IQ3Z |

| 廠商: | Cirrus Logic Inc |

| 文件頁數(shù): | 27/47頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC LINE INTERFACE T1/E1 64LQFP |

| 標(biāo)準(zhǔn)包裝: | 160 |

| 接口: | 并行/串行 |

| 電源電壓: | 3.3V,5V |

| 封裝/外殼: | 64-LQFP |

| 供應(yīng)商設(shè)備封裝: | 64-LQFP(10x10) |

| 包裝: | 托盤 |

| 安裝類型: | 表面貼裝 |

| 產(chǎn)品目錄頁面: | 759 (CN2011-ZH PDF) |

| 其它名稱: | 598-1713 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁當(dāng)前第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁

CS61584A

DS261PP5

33

DS261PP5

Bypass Register: The Bypass register consists of a

single bit, and provides a serial path between J-TDI

and J-TDO, bypassing the BSR. This allows by-

passing specific devices during certain board-level

tests. This also reduces test access times by reduc-

ing the total number of shifts required from J-TDI

to J-TDO.

10.2

JTAG Instructions and Instruction

Register (IR)

The instruction register (2 bits) allows the instruc-

tion to be shifted into the JTAG circuit. The in-

struction selects the test to be performed or the data

register to be accessed or both. The valid instruc-

tions are shifted in LSB first and are listed in

Table 12:

EXTEST Instruction: The EXTEST instruction al-

lows testing of off-chip circuitry and board-level

interconnect. EXTEST connects the BSR to the J-

TDI and J-TDO pins. The normal path between the

CS61584A logic and I/O pins is broken. The sig-

nals on the output pins are loaded from the BSR

and the signals on the input pins are loaded into the

BSR.

SAMPLE/PRELOAD

Instruction:

The

SAM-

PLE/PRELOAD instructions allows scanning of

the boundary-scan register without interfering with

the operation of the CS61584A. This instruction

connects the BSR to the J-TDI and J-TDO pins.

The normal path between the CS61584A logic and

its I/O pins is maintained. The signals on the I/O

pins are loaded into the BSR. Additionally, this in-

struction can be used to latch values into the digital

output pins.

IDCODE Instruction: The IDCODE instruction

connects the device identification register to the J-

TDO pin. The IDCODE instruction is forced into

the instruction register during the Test-Logic-Reset

controller state.The default instruction is IDCODE

after a device reset.

BYPASS Instruction: The BYPASS instruction

connects the minimum length bypass register be-

tween the J-TDI and J-TDO pins and allows data to

be shifted in the Shift-DR controller state.

10.3

JTAG TAP Controller

Figure 24 shows the state diagram for the TAP state

machine. A description of each state follows. Note

that the figure contains two main branches to ac-

cess either the data or instruction registers. The val-

ue shown next to each state transition in this figure

is the value present at J-TMS at each rising edge of

J-TCK.

10.4

Test-Logic-Reset State

In this state, the test logic is disabled to continue

normal operation of the device. During initializa-

tion, the CS61584A initializes the instruction reg-

ister with the IDCODE instruction.

Regardless of the original state of the controller,

the controller enters the Test-Logic-Reset state

when the J-TMS input is held high for at least five

rising edges of J-TCK. The controller remains in

this state while J-TMS is high. The CS61584A pro-

cessor automatically enters this state at power-up.

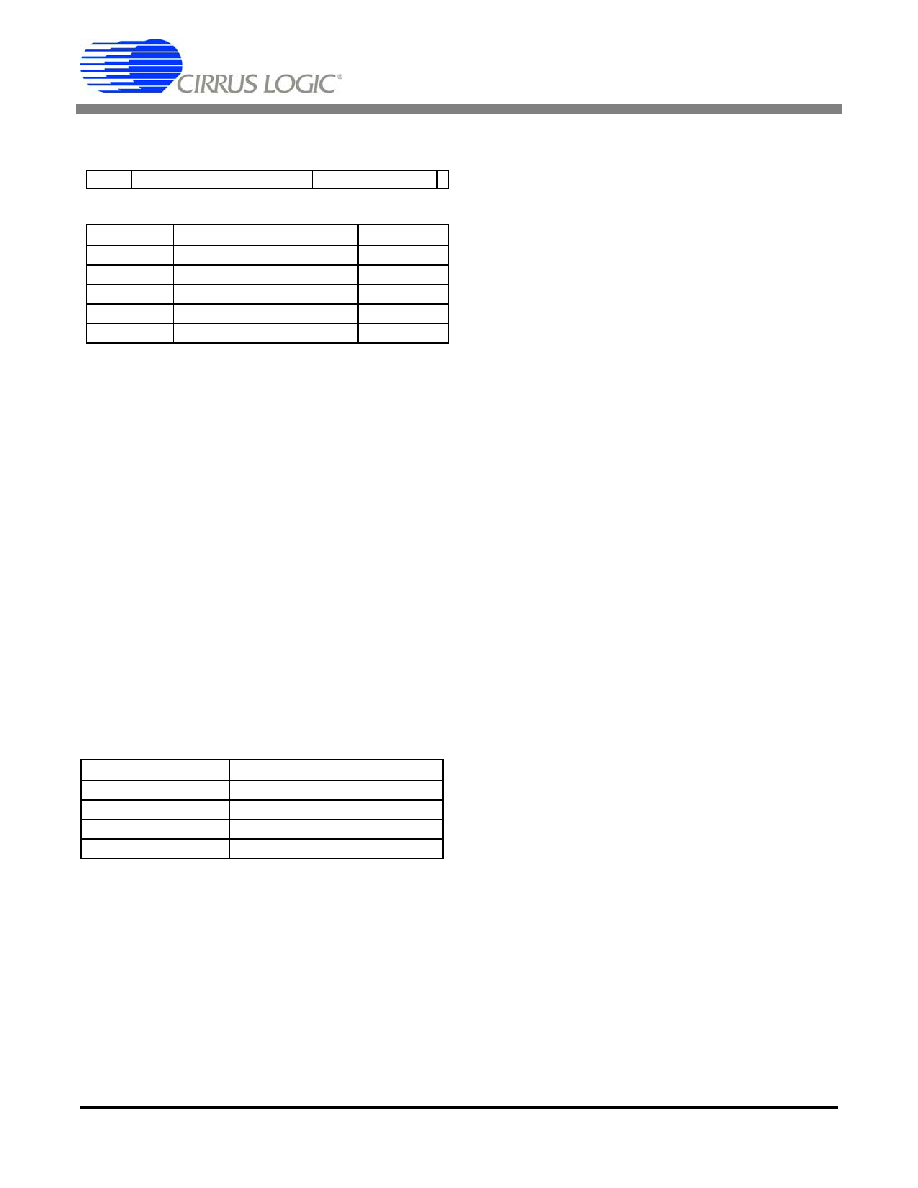

IR CODE

INSTRUCTION

00

EXTEST

01

SAMPLE/PRELOAD

10

IDCODE

11

BYPASS

Table 12.

MSB

LSB

31 28 27

12 11

1 0

0 00001 10011 011100 00100 00110 01001

4 bits

16 bits

11 bits

BIT #(s)

Function

Total Bits

31-28

Version Number

4

27-14

Part Number

14

13-12

Derivative Code

2

11-1

Manufacturer Number

11

0

Constant Logic ‘1’

1

Table 11. Device Identification Register

CS61584A

DS261F1

33

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CS61884-IRZ | IC LN INTERF T1/E1/J1 160-LFBGA |

| CS8130-CS | IC IR TRANSCEIVER 2-5V 20-SSOP |

| CS8190EDWF20G | IC TACH/SPEEDO DRVR PREC 20SOICW |

| CS8191XNF16 | IC DRVR AIRCORE TACH/SPEED 16DIP |

| CS82C5296 | IC UART/BRG 5V 16MHZ 28-PLCC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CS61584A-IQ3ZR | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC IC 3.3V/5V Dul T1/E1 Line Intrfc Unit RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| CS61584A-IQ5 | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC IC 3.3V/5V Dual T1/ E1 Line Intrfc Unit RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| CS61584A-IQ5Z | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC IC 3.3V/5V Dual T1/ E1 Line Intrfc Unit RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| CS61584A-IQ5ZR | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC IC 3.3V/5V Dul T1/E1 Line Intrfc Unit RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| CS61584-IL3 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Line Interface |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。