- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄375306 > AM49BDS640AHE8I (SPANSION LLC) Stacked Multichip Package (MCP), Flash Memory and pSRAM CMOS 1.8 Volt-only Simultaneous Read/Write PDF資料下載

參數(shù)資料

| 型號: | AM49BDS640AHE8I |

| 廠商: | SPANSION LLC |

| 元件分類: | 存儲器 |

| 英文描述: | Stacked Multichip Package (MCP), Flash Memory and pSRAM CMOS 1.8 Volt-only Simultaneous Read/Write |

| 中文描述: | SPECIALTY MEMORY CIRCUIT, PBGA89 |

| 封裝: | 10 X 8 MM, FBGA-89 |

| 文件頁數(shù): | 29/84頁 |

| 文件大小: | 763K |

| 代理商: | AM49BDS640AHE8I |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁當(dāng)前第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁

December 5, 2003

Am49BDS640AH

27

A D V A N C E I N F O R M A T I O N

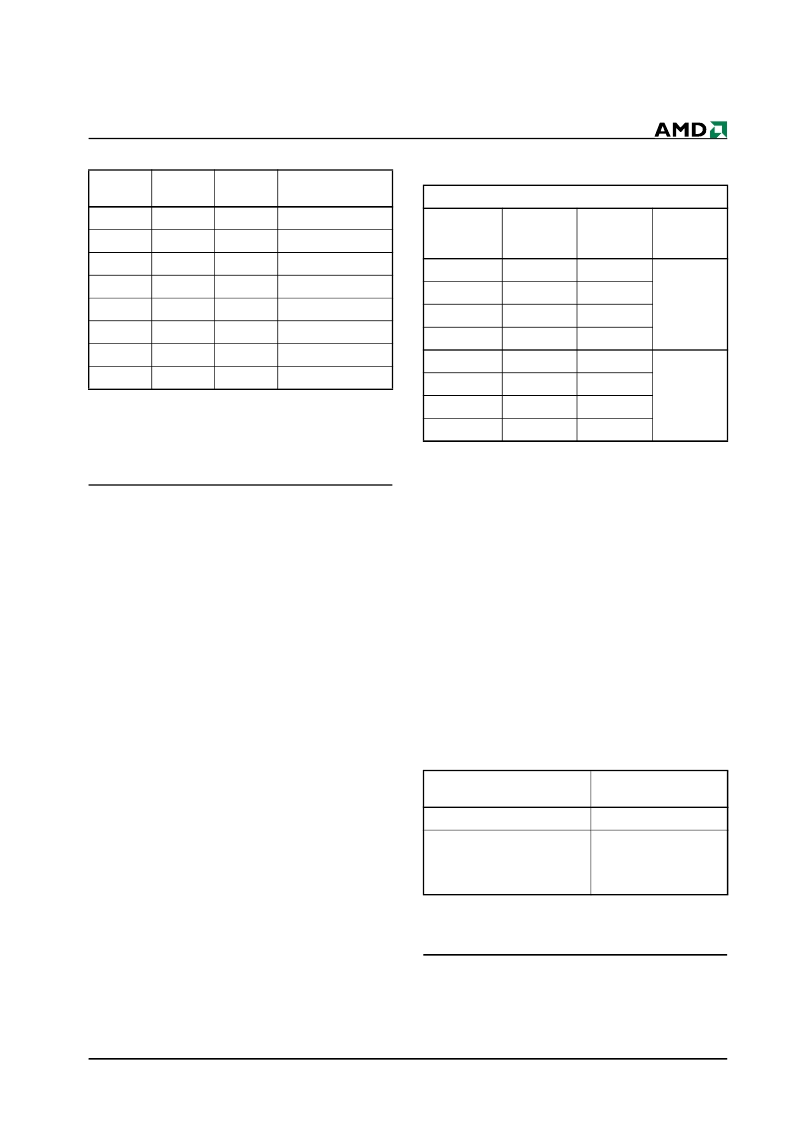

Table 10.

Programmable Wait State Settings

Notes:

1. Upon power-up or hardware reset, the default setting is

seven wait states.

2. RDY will default to being active with data when the Wait

State Setting is set to a total initial access cycle of 2.

It is recommended that the wait state command

sequence be written, even if the default wait state value

is desired, to ensure the device is set as expected. A

hardware reset will set the wait state to the default set-

ting.

Reduced Wait-state Handshaking Option

If the device is equipped with the reduced wait-state

handshaking option, the host system should set

address bits A14–A12 to 010 for the system/device to

execute at maximum speed.

Table 11

describes the typical number of clock cycles

(wait states) for various conditions.

Table 11.

Wait States for Reduced wait-state

Handshaking

Notes:

1. If the latched address is 3Eh or 3Fh (or an address offset

from either address by a multiple of 64), add two access

cycles to the values listed.

2. In the 8-, 16-, and 32-word burst modes, the address

pointer does not cross 64-word boundaries (3Fh, or

addresses offset from 3Fh by a multiple of 64).

3. Typical initial access cycles may vary depending on

system margin requirements.

Standard Handshaking Option

For optimal burst mode performance on devices with

the standard handshaking option, the host system

must set the appropriate number of wait states in the

flash device depending on the clock frequency.

Table 12

describes the typical number of clock cycles

(wait states) for various conditions with A14-A12 set to

101.

Table 12.

Wait States for Standard Handshaking

* In the 8-, 16- and 32-word burst read modes, the address

pointer does not cross 64-word boundaries (addresses

which are multiples of 3Fh).

The autoselect function allows the host system to

determine whether the flash device is enabled for

handshaking. See the

“Autoselect Command

Sequence” section on page 29

for more information.

A14

A13

A12

Total Initial Access

Cycles

0

0

0

2

0

0

1

3

0

1

0

4

0

1

1

5

1

0

0

6

1

0

1

7 (default)

1

1

0

Reserved

1

1

1

Reserved

V

IO

= 1.8 V

System

Frequency

Range

Even Initial

Address

Odd Initial

Address

Device

Speed

Rating

6

–

22 MHz

2

2

D

(54 MHz)

22

–

28 MHz

2

3

28

–

43 MHz

3

4

43

–

54 MHz

4

5

6

–

28 MHz

2

2

E

(66 MHz)

28

–

35 MHz

2

3

35

–

53 MHz

3

4

53

–

66 MHz

4

5

Conditions at Address

Typical No. of Clock

Cycles after AVD# Low

Initial address

7

Initial address is 3E or 3Fh (or

offset from these addresses by

a multiple of 64) and is at

boundary crossing*

7

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AM49BDS640AHE9I | Stacked Multichip Package (MCP), Flash Memory and pSRAM CMOS 1.8 Volt-only Simultaneous Read/Write |

| AM49DL320BGT701 | Stacked Multi-Chip Package (MCP) Flash Memory and SRAM 32 Megabit (4 M x 8-Bit/2 M x 16-Bit) CMOS 3.0 Volt-only, Simultaneous |

| AM49DL320BGB701 | Stacked Multi-Chip Package (MCP) Flash Memory and SRAM 32 Megabit (4 M x 8-Bit/2 M x 16-Bit) CMOS 3.0 Volt-only, Simultaneous |

| AM49DL320BGB70IS | Stacked Multi-Chip Package (MCP) Flash Memory and SRAM 32 Megabit (4 M x 8-Bit/2 M x 16-Bit) CMOS 3.0 Volt-only, Simultaneous |

| AM49DL320BGB70IT | Stacked Multi-Chip Package (MCP) Flash Memory and SRAM 32 Megabit (4 M x 8-Bit/2 M x 16-Bit) CMOS 3.0 Volt-only, Simultaneous |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AM49BDS640AHE9I | 制造商:SPANSION 制造商全稱:SPANSION 功能描述:Stacked Multichip Package (MCP), Flash Memory and pSRAM CMOS 1.8 Volt-only Simultaneous Read/Write |

| AM49DL3208G | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Am49DL3208G - Stacked Multi-Chip Package (MCP) Flash Memory and pSRAM |

| AM49DL320BG | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Am49DL320BG - Stacked Multi-Chip Package (MCP) Flash Memory and SRAM |

| AM49DL320BGB701 | 制造商:SPANSION 制造商全稱:SPANSION 功能描述:Stacked Multi-Chip Package (MCP) Flash Memory and SRAM 32 Megabit (4 M x 8-Bit/2 M x 16-Bit) CMOS 3.0 Volt-only, Simultaneous |

| AM49DL320BGB701S | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:32 Megabit (4 M x 8-Bit/2 M x 16-Bit) CMOS 3.0 Volt-only, Simultaneous Operation Flash Memory and 32 Mbit (2M x 16-Bit) Pseudo Static RAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。