- 您現在的位置:買賣IC網 > PDF目錄16820 > XR17V358IB-E8-EVB (Exar Corporation)EVAL BOARD FOR XR17V358-E8 PDF資料下載

參數資料

| 型號: | XR17V358IB-E8-EVB |

| 廠商: | Exar Corporation |

| 文件頁數: | 60/68頁 |

| 文件大?。?/td> | 0K |

| 描述: | EVAL BOARD FOR XR17V358-E8 |

| 產品培訓模塊: | PCIe UARTs UART Product Overview |

| 標準包裝: | 1 |

| 主要目的: | 接口,UART |

| 嵌入式: | 否 |

| 已用 IC / 零件: | XR17V358 |

| 已供物品: | 板 |

| 相關產品: | 1016-1294-ND - IC UART PCIE OCTAL 176FPBGA |

| 其它名稱: | 1016-1296 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁當前第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁

XR17V358

63

REV. 1.0.4

HIGH PERFORMANCE OCTAL PCI EXPRESS UART

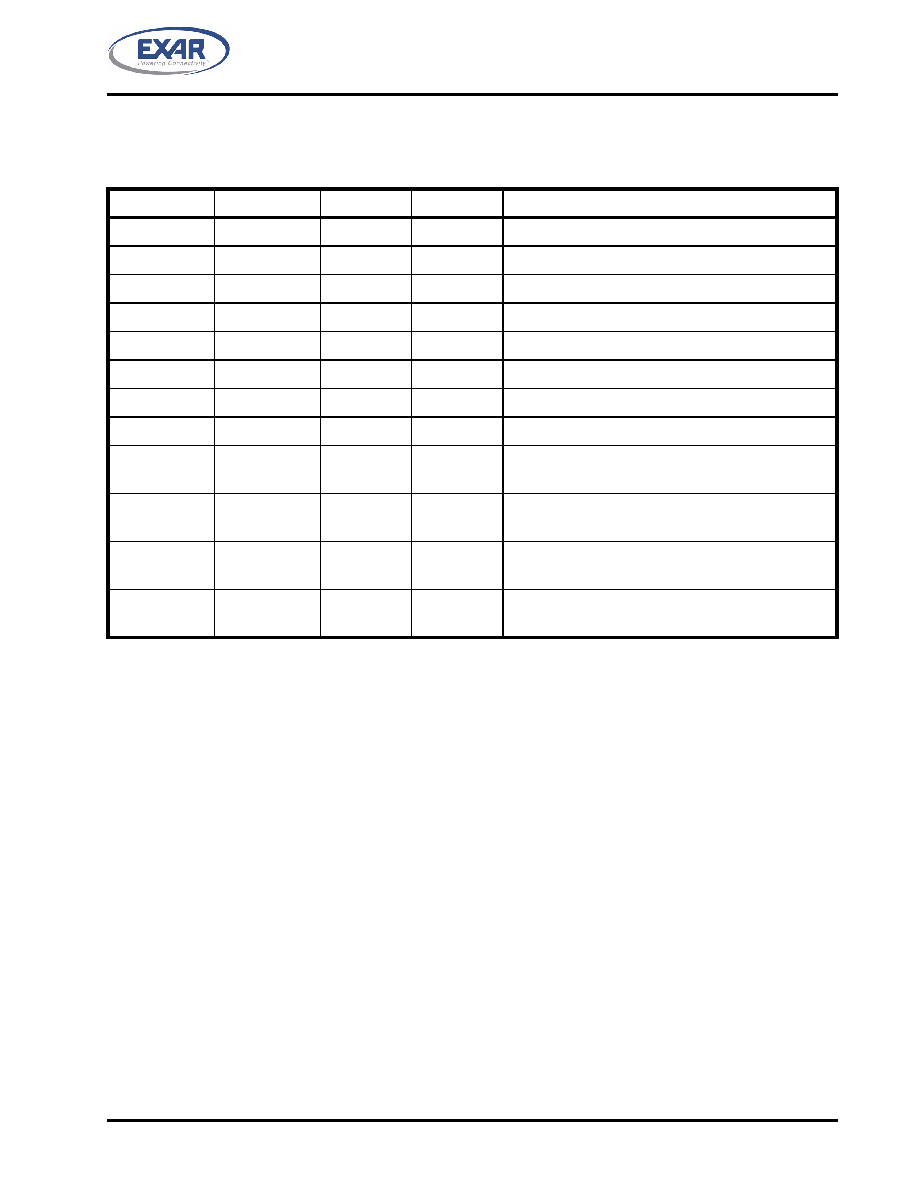

EFR[3:0]: Software Flow Control Select

Combinations of software flow control can be selected by programming these bits, as shown in Table 20.

TABLE 20: SOFTWARE FLOW CONTROL FUNCTIONS

TRANSMIT AND RECEIVE SOFTWARE FLOW CONTROL

0

No TX and RX flow control (default and reset)

0

X

No transmit flow control

1

0

X

Transmit Xon1, Xoff1

0

1

X

Transmit Xon2, Xoff2

1

X

Transmit Xon1 and Xon2, Xoff1 and Xoff2

X

0

No receive flow control

X

1

0

Receiver compares Xon1, Xoff1

X

0

1

Receiver compares Xon2, Xoff2

1

0

1

Transmit Xon1, Xoff1

Receiver compares Xon1 or Xon2, Xoff1 or Xoff2

0

1

Transmit Xon2, Xoff2

Receiver compares Xon1 or Xon2, Xoff1 or Xoff2

1

Transmit Xon1 and Xon2, Xoff1 and Xoff2

Receiver compares Xon1 and Xon2, Xoff1 and Xoff2

0

1

No transmit flow control

Receiver compares Xon1 and Xon2, Xoff1 and Xoff2

Software flow control can not be used when the Auto RS-485 Half-Duplex Direction Control feature is enabled

(FCTR[5]=1). With this feature enabled, the RTS#/DTR# output controls the direction of the half-duplex RS-

485 transceiver. The RTS#/DTR# output changes the direction of the half-duplex transceiver to the transmit

mode when data is being transmitted from the UART on the TX output. However, the RTS#/DTR# output will

remain in the receive direction if the TX FIFO is empty and the RX FIFO triggers an XON or XOFF character to

be transmitted.

4.15

TXCNT[7:0]: Transmit FIFO Level Counter - Read Only

Transmit FIFO level byte count from 0x00 (0 bytes) to 0xFF (255 or 256 bytes). This 8-bit register gives an

indication of the number of characters in the transmit FIFO. The FIFO level Byte count register is read only.

The user can take advantage of the FIFO level byte counter for faster data loading to the transmit FIFO, which

reduces CPU bandwidth requirements.

4.16

TXTRG [7:0]: Transmit FIFO Trigger Level - Write Only

An 8-bit value written to this register sets the TX FIFO trigger level from 0x00 (zero) to 0xFF (255). The TX

FIFO trigger level generates an interrupt whenever the data level in the transmit FIFO falls below this preset

trigger level.

4.17

RXCNT[7:0]: Receive FIFO Level Counter - Read Only

Receive FIFO level byte count from 0x00 (0 bytes) to 0xFF (255 or 256 bytes). It gives an indication of the

number of characters in the receive FIFO. The FIFO level byte count register is read only. The user can take

advantage of the FIFO level byte counter for faster data unloading from the receiver FIFO, which reduces CPU

bandwidth requirements.

EFR BIT [3]

EFR BIT [2]

EFR BIT [1]

EFR BIT [0]

相關PDF資料 |

PDF描述 |

|---|---|

| EBM24DCSH-S288 | CONN EDGECARD 48POS .156 EXTEND |

| EGM08DRST | CONN EDGECARD 16POS DIP .156 SLD |

| V150B28E150BL | CONVERTER MOD DC/DC 28V 150W |

| HSM06DRYH-S13 | CONN EDGECARD 12POS .156 EXTEND |

| EBM24DCSD-S288 | CONN EDGECARD 48POS .156 EXTEND |

相關代理商/技術參數 |

參數描述 |

|---|---|

| XR1857SN | 制造商:Electro-Term/Hollingsworth 功能描述: |

| XR1858SN | 制造商:Electro-Term/Hollingsworth 功能描述: |

| XR1859SN | 制造商:Electro-Term/Hollingsworth 功能描述: |

| XR1859SNT | 制造商:Hollingsworth 功能描述: |

| XR1880S | 制造商:Electro-Term/Hollingsworth 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復。