- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄231500 > WEDPNF8M722V-1015BI (WHITE ELECTRONIC DESIGNS CORP) SPECIALTY MEMORY CIRCUIT, PBGA275 PDF資料下載

參數(shù)資料

| 型號(hào): | WEDPNF8M722V-1015BI |

| 廠商: | WHITE ELECTRONIC DESIGNS CORP |

| 元件分類(lèi): | 存儲(chǔ)器 |

| 英文描述: | SPECIALTY MEMORY CIRCUIT, PBGA275 |

| 封裝: | 32 X 25 MM, PLASTIC, BGA-275 |

| 文件頁(yè)數(shù): | 10/43頁(yè) |

| 文件大小: | 1280K |

| 代理商: | WEDPNF8M722V-1015BI |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)當(dāng)前第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)

18

White Electronic Designs Corporation Phoenix AZ (602) 437-1520

White Electronic Designs

WEDPNF8M722V-XBX

The autoselect mode provides sector protection verifica-

tion, through identifier codes input codes output on FD7-

0. This mode is prima-rily intended for programming equip-

ment to automatically match a device to be programmed

with its corresponding programming algorithm. However,

the autoselect codes can also be accessed in-system

through the command register.

When using programming equipment, the autoselect mode

re-quires VID (11.5V to 12.5V) on address pin FA9. Ad-

dress pins FA6, FA1, and FA0 must be as shown in Table 6.

In addition, when verifying sector protection, the sector

address must appear on the appropriate highest order ad-

dress bits (see Table 5). Table 6 shows the remaining ad-

dress bits that are “don’t care.” When all necessary bits have

been set as required, the programming equip-ment may

then read the corresponding identifier code on FD7-0 or

FD23-16 .

To access the autoselect codes in-system, the host system

can issue the autoselect command via the command regis-

ter, as shown in Table 7. This method does not require VID.

See “Com-mand Definitions” for details on using the

autoselect mode.

AUTOSELECT MODE

TEMPORARY SECTOR UNPROTECT

This feature allows temporary unprotection of previously

protected sector groups to change data-in system. The

Sector Unprotect mode is activated by setting the RST pin

to VID. During this mode, formerly protected sector can

be programmed or erased by selecting the sector ad-

dresses. Once VID is removed from the RST pin, all the pre-

viously protected sector groups will be protected again.

Figure 16 shows the algorithm and the timing diagram is

shown in Figure 17, for this feature.

0.3V, the standby current will be greater.

The RST pin may be tied to the system reset circuitry. A

system reset would thus also reset the Flash memory, en-

abling the system to read the boot-up firmware from the

Flash memory.

If RST is asserted during a program or erase operation, RY/

BY1 pin remains “0” (busy) until the internal reset operation is

complete, which requires a time of tREADY (during Embed-

ded Algorithms). The system can thus monitor RY/BY1-2 to

determine whether the reset operation is complete. If RST is

asserted when a program or erase operation is not execut-

ing (RY/BY1-2 pins are “1”), the reset operation is completed

within a time of tREADY (not during Embedded Algorithms).

The system can read data tRH after the RST pin returns to VIH.

Refer to the Flash DC Characteristics and hardware reset tables

for RST parameters and to Figure 19 for the timing diagram.

HARDWARE DATA PROTECTION

The command sequence requirement of unlock cycles for

programming or erasing provides data protection against

inadvertent writes (refer to Table 7 for command definitions).

In addition, the following hardware data protection mea-

sures prevent accidental erasure or programming, which

might otherwise be caused by spurious system level sig-

nals during Vcc power-up and power-down transitions, or

from system noise.

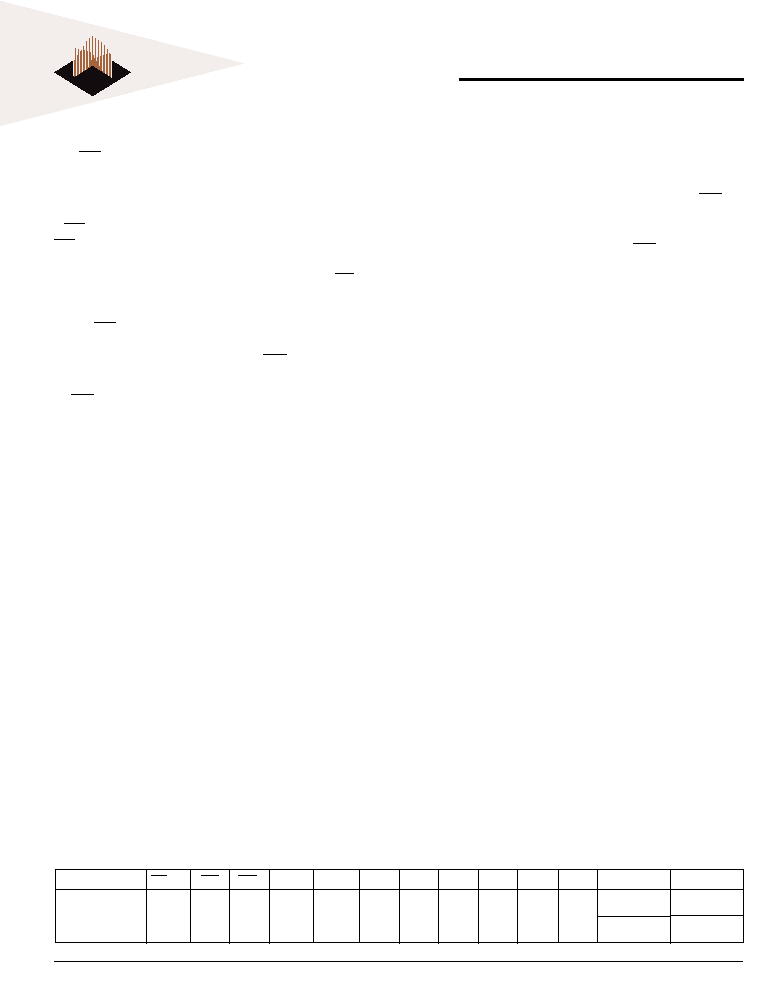

TABLE 6 - AUTOSELECT CODES (HIGH VOLTAGE METHOD)

Description

FCS1-2

FOE

FWE

FA

FA18

18

-----12

12

FA

FA11

11

-----10

10

FA

FA9

9

FA

FA8

8

-----7

7

FA

FA6

6

FA

FA5

5

-----2

2

FA

FA1

1

FA

FA0

0

FD

FD7

7

-----0

0

FD

FD23-16

23-16

Sector Protection

LL

H

SA

X

VID

XL

X

H

L

Verificaton

01h

(protected)

00h

(unprotected)

01h

(protected)

00h

(unprotected)

L = Logic Low = VIL, H = Logic High = VIH, SA = Sector Address, X = Don't Care

LOW VCC WRITE INHIBIT

When Vcc is less than VLKO, the device does not accept

any write cycles. This protects data during Vcc power-up

and power-down. The command register and all internal

program/erase circuits are disabled, and the device resets.

Subsequent writes are ignored until Vcc is greater than

VLKO. The system must provide the proper signals to the

control pins to prevent unintentional writes when Vcc is

greater than VLKO.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| W7NCF01GH30CS2BG | 64M X 16 FLASH 3.3V PROM CARD, 150 ns, UUC |

| W7NCF01GH30CS4AG | 64M X 16 FLASH 3.3V PROM CARD, 150 ns, UUC |

| W7NCF01GH30IS4BG | 64M X 16 FLASH 3.3V PROM CARD, 150 ns, UUC |

| W7NCF01GH30IS8FG | 64M X 16 FLASH 3.3V PROM CARD, 150 ns, UUC |

| W7NCF04GH10IS2EG | 256M X 16 FLASH 3.3V PROM CARD, 150 ns, UUC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| WEDPNF8M722V-1015BM | 制造商:WEDC 制造商全稱(chēng):White Electronic Designs Corporation 功能描述:8Mx72 Synchronous DRAM + 16Mb Flash Mixed Module Multi-Chip Package |

| WEDPNF8M722V-1210BC | 制造商:WEDC 制造商全稱(chēng):White Electronic Designs Corporation 功能描述:8Mx72 Synchronous DRAM + 16Mb Flash Mixed Module Multi-Chip Package |

| WEDPNF8M722V-1210BI | 制造商:WEDC 制造商全稱(chēng):White Electronic Designs Corporation 功能描述:8Mx72 Synchronous DRAM + 16Mb Flash Mixed Module Multi-Chip Package |

| WEDPNF8M722V-1210BM | 制造商:WEDC 制造商全稱(chēng):White Electronic Designs Corporation 功能描述:8Mx72 Synchronous DRAM + 16Mb Flash Mixed Module Multi-Chip Package |

| WEDPNF8M722V-1212BC | 制造商:WEDC 制造商全稱(chēng):White Electronic Designs Corporation 功能描述:8Mx72 Synchronous DRAM + 16Mb Flash Mixed Module Multi-Chip Package |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。