- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄225535 > W9412G6CH-5 (WINBOND ELECTRONICS CORP) 8M X 16 DDR DRAM, 0.7 ns, PDSO66 PDF資料下載

參數(shù)資料

| 型號: | W9412G6CH-5 |

| 廠商: | WINBOND ELECTRONICS CORP |

| 元件分類: | DRAM |

| 英文描述: | 8M X 16 DDR DRAM, 0.7 ns, PDSO66 |

| 封裝: | 0.400 INCH, 0.65 MM PITCH, ROHS COMPLIANT, TSOP2-66 |

| 文件頁數(shù): | 14/55頁 |

| 文件大小: | 2011K |

| 代理商: | W9412G6CH-5 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁當前第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁

W9412G6CH

Publication Release Date: Nov. 19, 2007

- 21 -

Revision A07

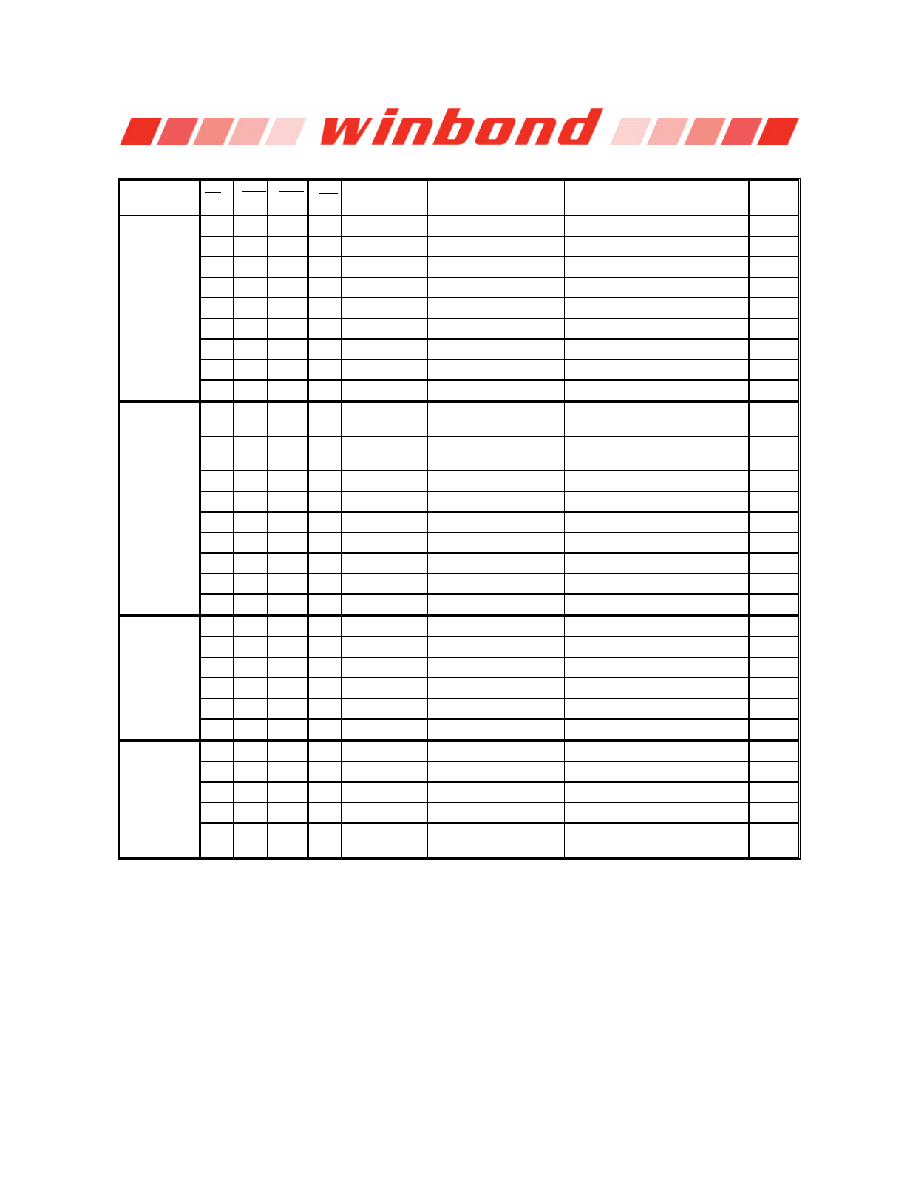

Function Truth Table, continued

CURRENT

STATE

CS

RAS CAS

WE

ADDRESS

COMMAND

ACTION

NOTES

H

X

DSL

NOP->Row active after tWR

L

H

X

NOP

NOP->Row active after tWR

L

H

L

X

BST

ILLEGAL

L

H

L

H

BS, CA, A10

READ/READA

ILLEGAL

3

L

H

L

BS, CA, A10

WRIT/WRITA

ILLEGAL

3

L

H

BS, RA

ACT

ILLEGAL

3

L

H

L

BS, A10

PRE/PREA

ILLEGAL

3

L

H

X

AREF/SELF

ILLEGAL

Write

Recovering

L

Op-Code

MRS/EMRS

ILLEGAL

H

X

DSL

NOP->Enter precharge after

tWR

L

H

X

NOP

NOP->Enter precharge after

tWR

L

H

L

X

BST

ILLEGAL

L

H

L

H

BS, CA, A10

READ/READA

ILLEGAL

3

L

H

L

BS, CA, A10

WRIT/WRITA

ILLEGAL

3

L

H

BS, RA

ACT

ILLEGAL

3

L

H

L

BS, A10

PRE/PREA

ILLEGAL

3

L

H

X

AREF/SELF

ILLEGAL

Write

Recovering

with Auto-

precharge

L

Op-Code

MRS/EMRS

ILLEGAL

H

X

DSL

NOP->Idle after TRC

L

H

X

NOP

NOP->Idle after TRC

L

H

L

X

BST

ILLEGAL

L

H

L

H

X

READ/WRIT

ILLEGAL

L

H

X

ACT/PRE/PREA

ILLEGAL

Refreshing

L

X

AREF/SELF/MRS/EMRS

ILLEGAL

H

X

DSL

NOP->Row after tMRD

L

H

X

NOP

NOP->Row after tMRD

L

H

L

X

BST

ILLEGAL

L

H

L

X

READ/WRIT

ILLEGAL

Mode

Register

Accessing

L

X

ACT/PRE/PREA/ARE

F/SELF/MRS/EMRS

ILLEGAL

Notes

:

1. All entries assume that CKE was active (High level) during the preceding clock cycle and the current clock cycle.

2. Illegal if any bank is not idle.

3. Illegal to bank in specified states; Function may be legal in the bank indicated by Bank Address (BS), depending on the

state of that bank.

4. Illegal if tRCD is not satisfied.

5. Illegal if tRAS is not satisfied.

6. Must satisfy burst interrupt condition.

7. Must avoid bus contention, bus turn around, and/or satisfy write recovery requirements.

8. Must mask preceding data which don’t satisfy tWR

Remark: H = High level, L = Low level, X = High or Low level (Don’t Care), V = Valid data

相關PDF資料 |

PDF描述 |

|---|---|

| W942504CH-7 | 64M X 4 DDR DRAM, 0.75 ns, PDSO66 |

| W9864G6IH-6 | 4M X 16 DDR DRAM, 5 ns, PDSO54 |

| WA-1RX33-A4 | SNAP ACTING/LIMIT SWITCH |

| WA-A325CBM | Peripheral Interface |

| WA-A325CPC | Peripheral Interface |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| W9412G6IH | 制造商:WINBOND 制造商全稱:Winbond 功能描述:2M × 4 BANKS × 16 BITS DDR SDRAM |

| W9412G6IH-5 | 功能描述:IC DDR-400 SDRAM 128MB 66TSSOPII RoHS:是 類別:集成電路 (IC) >> 存儲器 系列:- 標準包裝:1,000 系列:- 格式 - 存儲器:EEPROMs - 串行 存儲器類型:EEPROM 存儲容量:4K (512 x 8) 速度:400kHz 接口:I²C,2 線串口 電源電壓:2.7 V ~ 5.5 V 工作溫度:-40°C ~ 85°C 封裝/外殼:8-SOIC(0.173",4.40mm 寬) 供應商設備封裝:8-MFP 包裝:帶卷 (TR) |

| W9412G6JH | 制造商:WINBOND 制造商全稱:Winbond 功能描述:2M ? 4 BANKS ? 16 BITS DDR SDRAM |

| W9412G6JH-4 | 制造商:Winbond Electronics Corp 功能描述:8*16B DDR1 制造商:Winbond Electronics Corp 功能描述:IC DDR SDRAM 128M 250MHZ 66TSOP |

| W9412G6JH-5 | 制造商:Winbond Electronics Corp 功能描述:DRAM Chip DDR SDRAM 128M-Bit 8Mx16 2.5V 66-Pin TSOP 制造商:Winbond Electronics Corp 功能描述:128M BIT DDR1 |

發(fā)布緊急采購,3分鐘左右您將得到回復。