- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359432 > VSC870 (VITESSE SEMICONDUCTOR CORP) High Performance Serial Backplane Transceiver PDF資料下載

參數(shù)資料

| 型號(hào): | VSC870 |

| 廠商: | VITESSE SEMICONDUCTOR CORP |

| 元件分類: | 通用總線功能 |

| 英文描述: | High Performance Serial Backplane Transceiver |

| 中文描述: | LINE TRANSCEIVER, PBGA192 |

| 封裝: | BGA-192 |

| 文件頁數(shù): | 19/40頁 |

| 文件大?。?/td> | 511K |

| 代理商: | VSC870 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁當(dāng)前第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁

VITESSE

Data Sheet

VSC870

High Performance Serial

Backplane Transceiver

G52190-0, Rev 4.1

01/05/01

Page 19

VITESSE

SEMICONDUCTOR CORPORATION

741 Calle Plano

Camarillo, CA 93012

Tel: (800) VITESSE

FAX: (805) 987-5896

Email: prodinfo@vitesse.com

Internet: www.vitesse.com

2), it stops reading from the parallel interface by setting REN LOW, sets RTM/TCLK HIGH and starts sending a

repeated sequence of CRQ words to the switch which are arbitrated only on the cycle that they arrive. During this

operation, the CRQ words are not stored at the switch. If all connections are granted, the transceiver will receive an

ACK from the switch. If DLYEN/CCKIN is LOW, it sets the REN signal HIGH when it receives the ACK, and sends

the header word and data to the switch. If DLYEN/CCKIN is HIGH, it waits for N more cycles before it sets REN

HIGH and then sends header word and data to the switch.

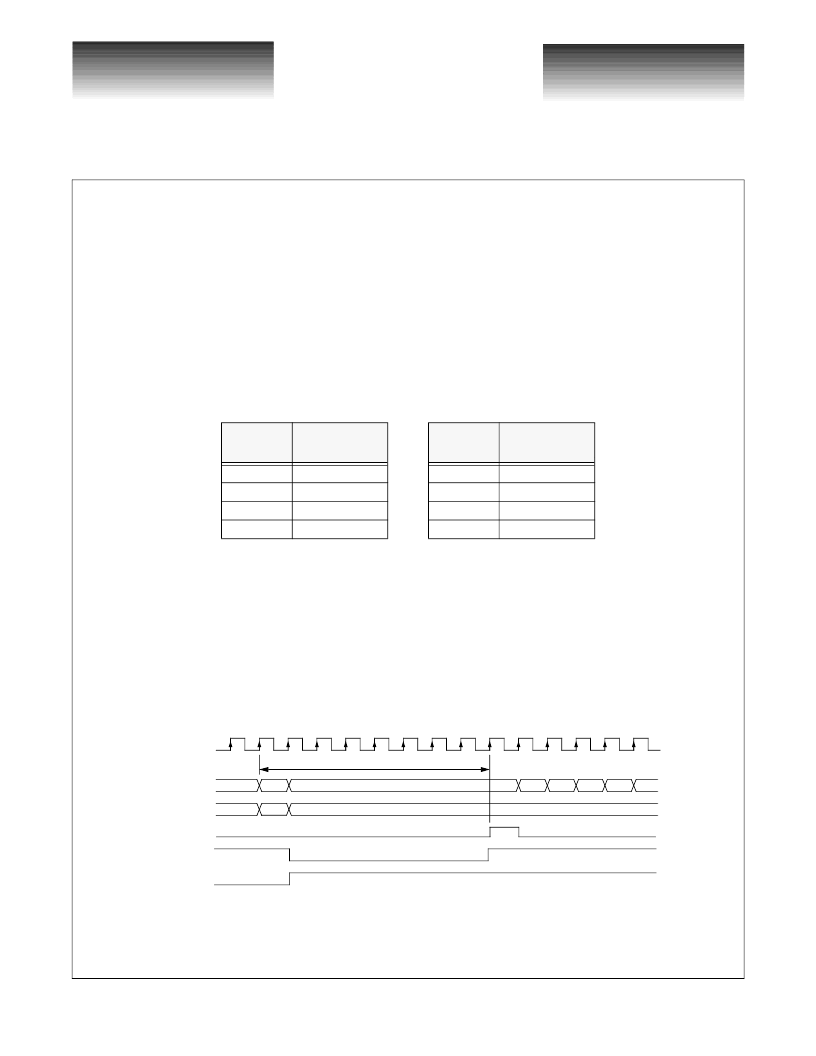

During the repeated sequence of CRQs described above, different priorities for connections can be established by

the number of the IDLE words sent between each CRQ words (determined by the CT[2:0]). The number of IDLEs

after each CRQ word can range from 0-7 as shown in the table below. Generally, the more often a CRQ is received by

the switch, the higher the probability that this connection will be granted.

The functional timing diagram for camp-on mode with DLYEN/CCKIN set LOW is shown in figure 3. There are

a minimum of 9 word clock cycles between loading the CRQ into the transceiver and the signal REN going HIGH (to

start sending the data packet D0, D1, D2 etc.). This time will be longer if the requested output is busy or the port card

is located further from the switch card. For multicast, the switch will reserve any available outputs and accumulate

them as more CRQ commands are processed. This continues until all connections are reserved. At this point an ACK

signal is sent back to the transceiver.

Figure 3: Camp-on with Priority Transmitter Functional Timing (no early arbitration)

CT[2:0]

Number of

IDLE Words

CT[2:0]

Number of

IDLE Words

0 0 0

0 0 1

0 1 0

0 1 1

0

1

2

3

1 0 0

1 0 1

1 1 0

1 1 1

4

5

6

7

WCLK

TXIN[31:0]

TXTYP[1:0]

REN

ACK/RCLK

CRQ

D0

D1

D2

D3

D4

D5

3

2

Minimum of 9 clock cycles

RTM/TCLK

1

HDR

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| VSC870TX | High Performance Serial Backplane Transceiver |

| VSC872 | 80 Gb/s Intelligent Switch Fabric |

| VSC874 | 10 Gbps Queue Manager with Integrated SPI4.2 Interface |

| VSC880 | High Performance 16x16 Serial Crosspoint Switch |

| VSC9110 | Target Specification |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| VSC870TX | 制造商:VITESSE 制造商全稱:Vitesse Semiconductor Corporation 功能描述:High Performance Serial Backplane Transceiver |

| VSC872 | 制造商:VITESSE 制造商全稱:Vitesse Semiconductor Corporation 功能描述:80 Gb/s Intelligent Switch Fabric |

| VSC872TV01 | 制造商:Vitesse Semiconductor Corporation 功能描述: |

| VSC874 | 制造商:VITESSE 制造商全稱:Vitesse Semiconductor Corporation 功能描述:10 Gbps Queue Manager with Integrated SPI4.2 Interface |

| VSC880 | 制造商:VITESSE 制造商全稱:Vitesse Semiconductor Corporation 功能描述:High Performance 16x16 Serial Crosspoint Switch |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。