- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384047 > UPD98409GN-LMU (NEC Corp.) ATM LIGHT SAR CONTROLLER PDF資料下載

參數(shù)資料

| 型號: | UPD98409GN-LMU |

| 廠商: | NEC Corp. |

| 英文描述: | ATM LIGHT SAR CONTROLLER |

| 中文描述: | 自動柜員機(jī)燈特區(qū)控制器 |

| 文件頁數(shù): | 9/36頁 |

| 文件大?。?/td> | 402K |

| 代理商: | UPD98409GN-LMU |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁當(dāng)前第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁

9

μ

PD98409

(2/2)

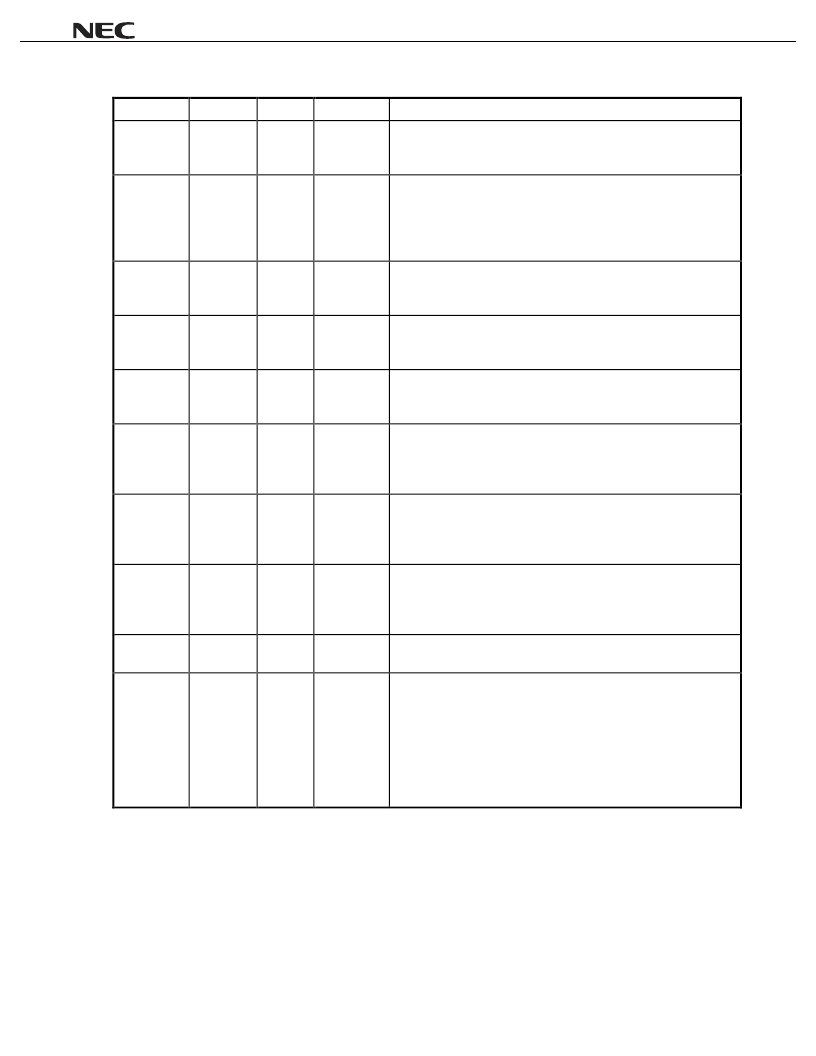

Pin Name

Pin No.

I/O

I/O Level

Function

STOP_B

34

I/O

Sustained

3-state

PCI

Stop.

This signal goes low when the target device requests the master

device to stop the current transaction.

DEVSEL_B

33

I/O

Sustained

3-state

PCI

Device select.

This signal goes low when the

μ

PD98409 operates as a target and

recognizes an address after the FRAME_B signal has become active.

When the

μ

PD98409 operates as the master, it samples this signal to

check to see whether a target device has been selected.

IDSEL

13

I

PCI

Initialization device select.

This signal inputs a high level when the configuration register of the

μ

PD98409 is read/written.

REQ_B

69

O

Note

PCI

Request.

The

μ

PD98409 requests the arbiter for the bus mastership by making

this signal low.

GNT_B

71

I

PCI

Grant.

This signal goes low when the arbiter grants the

μ

PD98409 the bus

mastership.

PERR_B

35

I/O

Sustained

3-state

PCI

Parity error.

This signal indicates that the

μ

PD98409 has detected a parity error. It

is enabled when the “Parity Error Response” bit of the configuration

register is set to 1.

SERR_B

37

O

N-ch

open-drain

System error.

This signal indicates that the

μ

PD98409 has detected an address

parity error. It is enabled when both the “Parity Error Response” and

“System Error Enable” bits of the configuration register are set to 1.

INTR_B

75

O

N-ch

open-drain

Interrupt output.

Pull up this pin because it outputs an open-drain signal. INTR_B

informs the CPU that the interrupt bit (not masked) of the GSR register

is set.

BUSCLK

73

I

PCI

PCI bus clock.

Bus clock input pin. It inputs a clock of up to 33 MHz.

RST_B

235

I

PCI

Reset.

The RST_B signal initializes the

μ

PD98409 (on starting). When a low

level is input to RST_B, the internal state machine and registers of the

μ

PD98409 are reset, and all the 3-state signals go into a high-

impedance state. When this signal is input while the

μ

PD98409 is

operating, the operating status at that time is lost. Keep the input to

RST_B low at least for the duration of 1 clock cycle. Do not access

the

μ

PD98409 at least for 20 clocks after it has been reset.

Note

Although the “PCI Local Bus Specification Revision 2.1” specifies that the REQ_B pin go into a high-

impedance state while a low level is input to the RST_B pin, the REQ_B pin of the

μ

PD98409 outputs a

high level.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| UPD98409 | ATM LIGHT SAR CONTROLLER |

| UPG158TB-E3 | L, S- BAND SPDT SWITCH |

| UPG158 | L, S- BAND SPDT SWITCH |

| UPG158TB | L, S- BAND SPDT SWITCH |

| UPG2009TB | NECs L, S-BAND 4W SPDT SWITCH |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| UPD98411 | 制造商:NEC 制造商全稱:NEC 功能描述:ATM QUAD SONET FRAMER |

| UPD98411GN-MMU | 制造商:NEC 制造商全稱:NEC 功能描述:ATM QUAD SONET FRAMER |

| UPD98412 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Telecommunication IC |

| UPD98412N7-H6 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ATM DATA-LINK SWITCHING/ROUTING|CMOS|BGA|576PIN|PLASTIC |

| UPD98414 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Telecommunication IC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。