- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384047 > UPD98409GN-LMU (NEC Corp.) ATM LIGHT SAR CONTROLLER PDF資料下載

參數(shù)資料

| 型號: | UPD98409GN-LMU |

| 廠商: | NEC Corp. |

| 英文描述: | ATM LIGHT SAR CONTROLLER |

| 中文描述: | 自動柜員機燈特區(qū)控制器 |

| 文件頁數(shù): | 8/36頁 |

| 文件大小: | 402K |

| 代理商: | UPD98409GN-LMU |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁當(dāng)前第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁

8

μ

PD98409

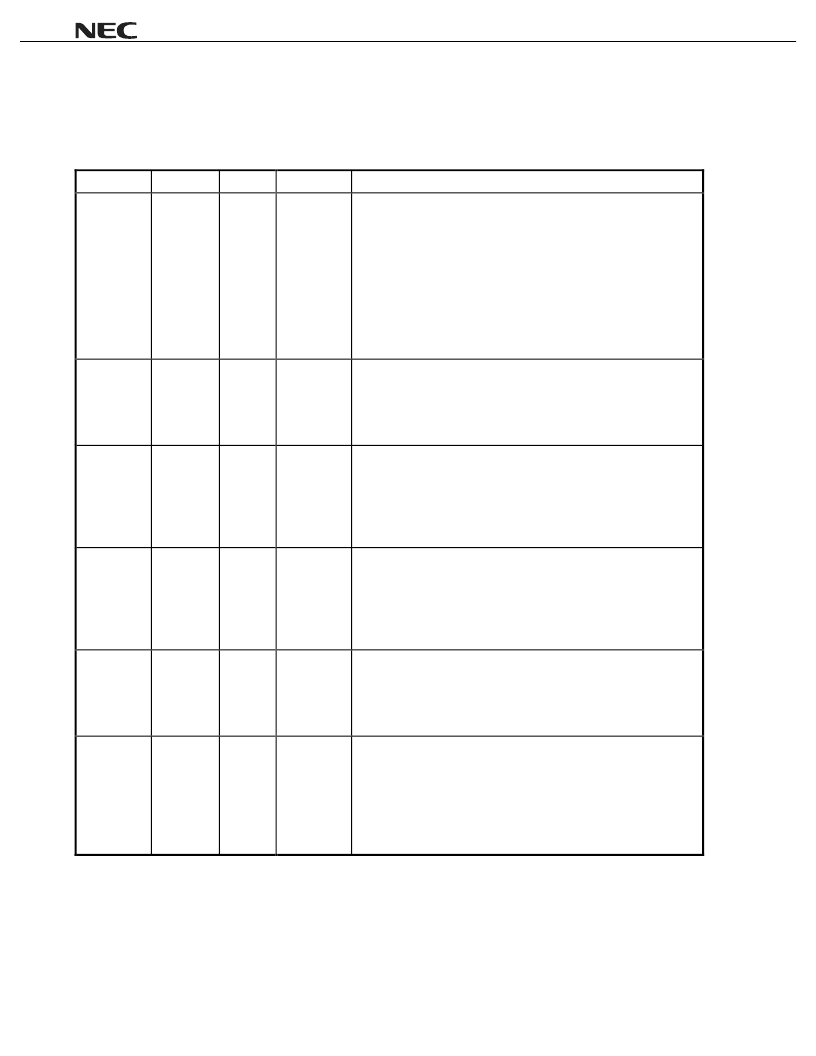

1.2 Bus Interface Pins

The

μ

PD98409 employs a 32-bit PCI bus interface as a bus interface with the host. This interface conforms to

“PCI Local Bus Specification Revision 2.1”.

(1/2)

Pin Name

Pin No.

I/O

I/O Level

Function

AD31-AD0

238, 239,

3 - 6,

9, 10,

16 - 19,

22 - 25,

42 - 45,

48 - 51,

55 - 57,

62 - 65,

68

I/O

3-state

PCI

Address/data.

AD31 through AD0 are 32 bits of multiplexed address and data bus

signals. When the

μ

PD98409 operates as the bus master, it drives an

address at the first one clock, and transfers data at the second clock

and onward.

PCBE3_B

PCBE2_B

PCBE1_B

PCBE0_B

11,

27,

39,

54

I/O

3-state

PCI

Bus command and byte enable.

These signals define “bus commands” (generated bus transaction) in an

address phase. In a data phase, they indicate which byte lane holds

valid data. The PCBE3_B pin corresponds to byte 3 (bits 31 through

24), and PCBE0_B pin corresponds to byte 0 (bits 7 through 0).

PAR

38

I/O

3-state

PCI

Parity.

This signal inputs/outputs an even parity on the AD31 through AD0

and PCBE3_B through PCBE0_B pins including the PAR signal.

When the

μ

PD98409 operates as the master, the PAR signal is output

in the address and write data phases. When the

μ

PD98409 operates

as a target, the PAR signal is output in the read data phase.

FRAME_B

28

I/O

Sustained

3-state

PCI

Frame.

This signal indicates the start and period of bus transaction. When

this signal becomes active, it indicates the start of bus transaction.

While it is active, data is transferred. When the next data transfer

phase is for the last data of the transaction, this signal becomes

inactive.

TRDY_B

30

I/O

Sustained

3-state

PCI

Target ready.

This signal goes low when the target device is ready to complete the

transaction of the current data phase. This signal is used in pairs with

IRDY_B. When both IRDY_B and TRDY_B are low, read/write data

transfer is executed.

IRDY_B

29

I/O

Sustained

3-state

PCI

Initiator ready.

This signal goes low when the initiator is ready to complete the

transaction of the current data phase. This signal is used in pairs with

TRDY_B. When both IRDY_B and TRDY_B are low, read/write data

transfer is executed. If both FRAME_B and IRDY_B are inactive, the

bus cycle is not executed, and wait cycles are inserted until both

IRDY_B and TRDY_B become active.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| UPD98409 | ATM LIGHT SAR CONTROLLER |

| UPG158TB-E3 | L, S- BAND SPDT SWITCH |

| UPG158 | L, S- BAND SPDT SWITCH |

| UPG158TB | L, S- BAND SPDT SWITCH |

| UPG2009TB | NECs L, S-BAND 4W SPDT SWITCH |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| UPD98411 | 制造商:NEC 制造商全稱:NEC 功能描述:ATM QUAD SONET FRAMER |

| UPD98411GN-MMU | 制造商:NEC 制造商全稱:NEC 功能描述:ATM QUAD SONET FRAMER |

| UPD98412 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Telecommunication IC |

| UPD98412N7-H6 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ATM DATA-LINK SWITCHING/ROUTING|CMOS|BGA|576PIN|PLASTIC |

| UPD98414 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Telecommunication IC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。