- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384039 > UPC1854AGT (NEC Corp.) I2C BUS-COMPATIBLE US MTS PROCESSING LSI PDF資料下載

參數(shù)資料

| 型號: | UPC1854AGT |

| 廠商: | NEC Corp. |

| 英文描述: | I2C BUS-COMPATIBLE US MTS PROCESSING LSI |

| 中文描述: | I2C總線兼容美國的多邊貿(mào)易體制處理LSI |

| 文件頁數(shù): | 37/48頁 |

| 文件大小: | 251K |

| 代理商: | UPC1854AGT |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁當(dāng)前第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁

μ

PC1854A

37

Data Sheet S12816EJ3V0DS00

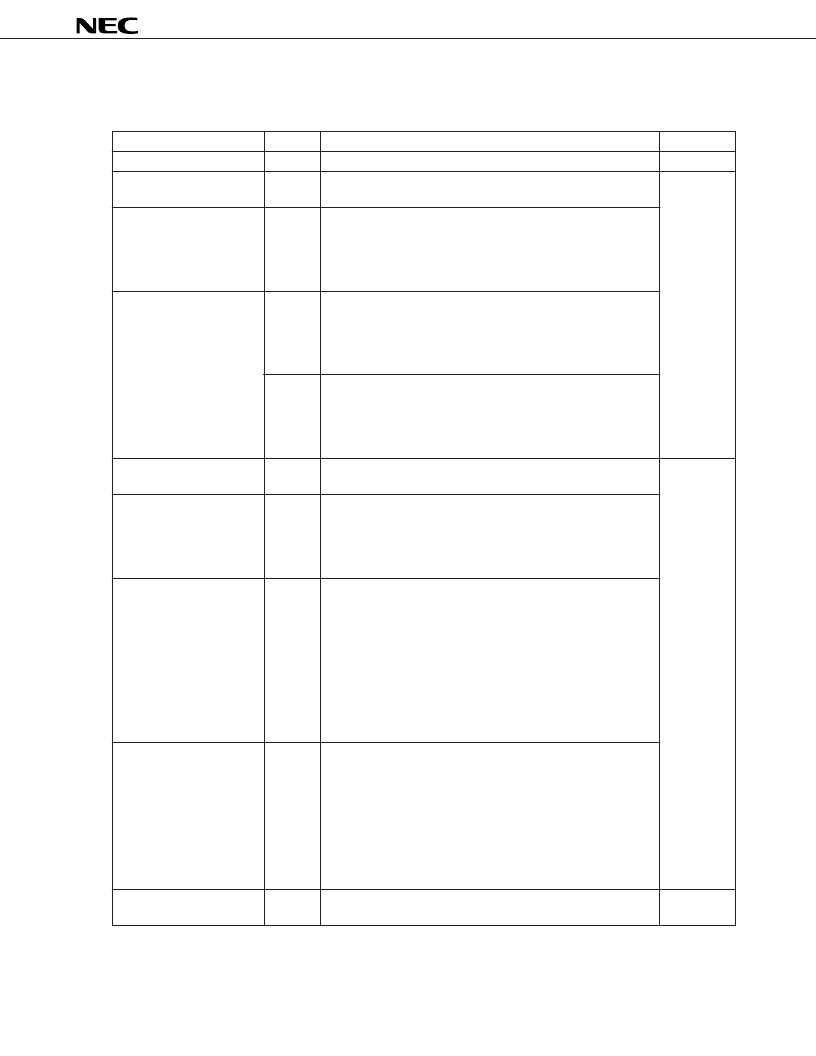

Test Condition Parameters for Electrical Characteristics

(Unless otherwise specified, T

A

= 25

°

C, RH

≤

70 %, V

CC

= 9 V)

(1/7)

Parameter

Symbol

Test Conditions

User Mode

Note

Supply current

I

CC

I

CC

: Current sent to V

CC

pin when there is no signal

Monaural

Stereo detection input

sensitivity

ST

SENCE

ST

SENCE

: Input signal level of COM pin (input signal: 15.734 kHz)

Read register D6 : when changed from 0 to 1

Stereo

Stereo detection hysteresis

ST

HY

ST

HY

=20 log (ST

SENCE

÷

V)

ST

SENCE

: Stereo detection input sensitivity

V : Input signal level of COM pin (Input signal: 15.734 kHz)

Read register D6 : First set to 1, then changed to 0 by gradually

lowering input signal level.

Stereo detection

capture range

ST

CCL

ST

CCL

=

f

÷

15.734 kHz

f : Difference between f and 15.734 kHz

f : With signal (14.5 kHz, 30 mV

rms

) input to COM pin;

The frequency, which is gradually raised and measured when

read register D6 becomes 1

ST

CCH

ST

CCH

=

f

÷

15.734 kHz

f : Difference between f and 15.734 kHz

f : With signal (17.0 kHz, 30 mV

rms

) input to COM pin;

The frequency, which is gradually lowered and measured when

read register D6 becomes 1

SAP detection input

sensitivity

SAP

SENCE

SAP

SENCE

: Input signal level of COM pin (input signal: 78.67 kHz)

Read register D5 : when changed from 0 to 1

SAP

SAP detection hysteresis

SAP

HY

SAP

HY

=20 log (SAP

SENCE

÷

V)

SAP

SENCE

: SAP detection input sensitivity

V: Input signal level of COM pin (Input signal: 78.67 kHz)

Read register D5 : First set to 1, then changed to 0 by gradually

lowering input signal level.

Noise detection input

sensitivity

NO

SENCE

NO

SENCE

: Input signal level of COM pin

Read register D4 : Changed to 0 by applying 6-V DC voltage to

SDT pin.

Read register D4 : With signal (160 kHz, 10 mVrms) input to

COM pin;

Changed to 1 by raising the frequency until

the DC voltage of the NDT pin reaches the

maximum level and, with maintaining this

frequency, gradually raising the input signal

level.

Noise detection hysteresis

NO

HY

NO

HY

= 20 log (NO

SENCE

÷

V)

NO

SENCE

: Noise detection input sensitivity

V: Input signal level of NDT pin

COM pin : Signal (160 kHz, 90 mVrms) input

Read register D4 : First set to 1, then changed to 0 by raising

the frequency until the DC voltage of the

NDT pin reaches the maximum level and,

with maintaining this frequency, gradually

raising the input signal level.

Monaural total output voltage V

OMO

V

OMO

: Output voltage of ROT and LOT pins

COM pin: Monaural signal (300 Hz, 100% modulation) input

Monaural

Note

For details about the User Mode, refer to chapter

5. MODE MATRIX

.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| UPC1854ACT | I2C BUS-COMPATIBLE US MTS PROCESSING LSI |

| UPC1854A | I2C BUS-COMPATIBLE US MTS PROCESSING LSI |

| UPC1862 | BURST LOCK CLOCK GENERATOR |

| UPC1862GS | BURST LOCK CLOCK GENERATOR |

| UPC1883 | BIPOLAR ANALOG INTEGRATED CIRCUIT |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| UPC1857 | 制造商:NEC 制造商全稱:NEC 功能描述:SOUND CONTROL IC WITH SURROUND AND I2C BUS |

| UPC1857A | 制造商:NEC 制造商全稱:NEC 功能描述:SOUND CONTROL IC WITH SURROUND AND I2C BUS |

| UPC1857ACT | 制造商:NEC 制造商全稱:NEC 功能描述:SOUND CONTROL IC WITH SURROUND AND I2C BUS |

| UPC1860GS | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:TV/Video Sync Circuit |

| UPC1861 | 制造商:NEC 制造商全稱:NEC 功能描述:HORIZONTAL LOCK CLOCK GENERATOR |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。