- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98301 > TSC2003IR (TEXAS INSTRUMENTS INC) 3-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO16 PDF資料下載

參數(shù)資料

| 型號(hào): | TSC2003IR |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | ADC |

| 英文描述: | 3-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO16 |

| 封裝: | PLASTIC, TSSOP-16 |

| 文件頁(yè)數(shù): | 6/20頁(yè) |

| 文件大小: | 309K |

| 代理商: | TSC2003IR |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)當(dāng)前第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)

TSC2003

14

SBAS162A

www.ti.com

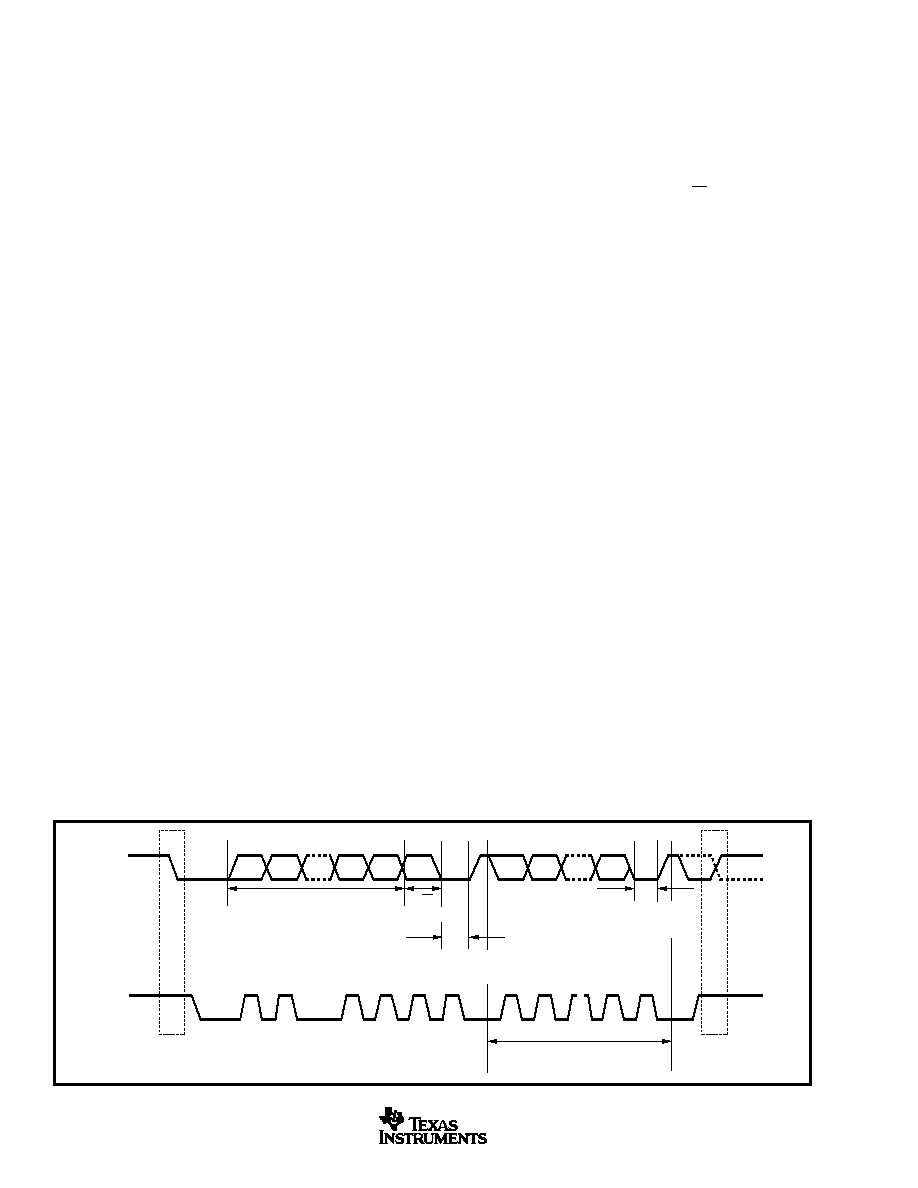

FIGURE 9. I2C Bus Protocol.

SDA

SCL

Slave Address

Repeated If More Bytes Are Transferred

R/W

Direction

Bit

Acknowledgement

Signal from

Receiver

Acknowledgement

Signal from

Receiver

START

Condition

12

7

6

8

9

1

2

3-7

8

9

ACK

STOP Condition

or Repeated

START Condition

generates the serial clock (SCL), controls the bus access, and

generates the START and STOP conditions. The TSC2003

operates as a slave on the I2C bus. Connections to the bus are

made via the open-drain I/O lines SDA and SDL.

The following bus protocol has been defined, as shown in

Figure 9:

Data transfer may be initiated only when the bus is not

busy.

During data transfer, the data line must remain stable

whenever the clock line is HIGH. Changes in the data line

while the clock line is HIGH will be interpreted as control

signals.

Accordingly, the following bus conditions have been defined:

Bus Not Busy: Both data and clock lines remain HIGH.

Start Data Transfer: A change in the state of the data line,

from HIGH to LOW, while the clock is HIGH defines a

START condition.

Stop Data Transfer: A change in the state of the data line,

from LOW to HIGH, while the clock line is HIGH defines

a STOP condition.

Data Valid: The state of the data line represents valid data

when, after a START condition, the data line is stable for the

duration of the HIGH period of the clock signal. There is one

clock pulse per bit of data.

Each data transfer is initiated with a START condition and

terminated with a STOP condition. The number of data bytes

transferred between START and STOP conditions is not

limited, and is determined by the master device. The infor-

mation is transferred byte-wise, and each receiver acknowl-

edges with a ninth-bit.

Within the I2C bus specifications, a standard mode (100kHz

clock rate), a fast mode (400kHz clock rate), and a

high-speed mode (3.4MHz clock rate) are defined. The

TSC2003 works in all three modes.

Acknowledge: Each receiving device, when accessed, is obliged

to generate an acknowledge after the reception of each byte. The

master device must generate an extra clock pulse which is

associated with this acknowledge bit.

A device that acknowledges must pull down the SDA line during

the acknowledge clock pulse in such a way that the SDA line is

stable LOW during the HIGH period of the acknowledge clock

pulse. Of course, setup and hold times must be taken into account.

A master must signal an end of data to the slave by not generating

an acknowledge bit on the last byte that has been clocked out of

the slave. In this case, the slave must leave the data line HIGH

to enable the master to generate the STOP condition.

Figure 9 details how data transfer is accomplished on the I2C

bus. Depending upon the state of the R/W bit, two types of

data transfer are possible:

Data transfer from a master transmitter to a slave receiver.

The first byte transmitted by the master is the slave address.

Next follows a number of data bytes. The slave returns an

acknowledge bit after the slave address and each received byte.

Data transfer from a slave transmitter to a master

receiver. The first byte (the slave address) is transmitted

by the master. The slave then returns an acknowledge bit.

Next, a number of data bytes are transmitted by the slave

to the master. The master returns an acknowledge bit

after all received bytes other than the last one. At the end

of the last received byte, a ‘not acknowledge’ is returned.

The master device generates all of the serial clock pulses and

the START and STOP conditions. A transfer is ended with

a STOP condition or a repeated START condition. Since a

repeated START condition is also the beginning of the next

serial transfer, the bus will not be released.

The TSC2003 may operate in the following two modes:

Slave Receiver Mode: Serial data and clock are received

through SDA and SCL. After each byte is received, an

acknowledge bit is transmitted. START and STOP con-

ditions are recognized as the beginning and end of a serial

transfer. Address recognition is performed by hardware

after reception of the slave address and direction bit.

Slave Transmitter Mode: The first byte (the slave ad-

dress) is received and handled as in the slave receiver

mode. However, in this mode the direction bit will

indicate that the transfer direction is reversed. Serial data

is transmitted on SDA by the TSC2003 while the serial

clock is input on SCL. START and STOP conditions are

recognized as the beginning and end of a serial transfer.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TSC2008IRGVR | SPECIALTY CONSUMER CIRCUIT, PQCC16 |

| TSC2008IRGVT | SPECIALTY CONSUMER CIRCUIT, PQCC16 |

| TSC2008IYZGR | SPECIALTY CONSUMER CIRCUIT, BGA12 |

| TSC2008IYZGT | SPECIALTY CONSUMER CIRCUIT, BGA12 |

| TSC2008TRGVRQ1 | SPECIALTY CONSUMER CIRCUIT, PQCC16 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TSC2003IZQCR | 功能描述:觸摸屏轉(zhuǎn)換器和控制器 4-wire Touch Screen Controller RoHS:否 制造商:Microchip Technology 類型:Resistive Touch Controllers 輸入類型:3 Key 數(shù)據(jù)速率:140 SPS 分辨率:10 bit 接口類型:4-Wire, 5-Wire, 8-Wire, I2C, SPI 電源電壓:2.5 V to 5.25 V 電源電流:17 mA 工作溫度:- 40 C to + 85 C 封裝 / 箱體:SSOP-20 |

| TSC2003-Q1 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:I2C TOUCH SCREEN CONTROLLER |

| TSC2004 | 制造商:BB 制造商全稱:BB 功能描述:1.2V to 3.6V, 12-Bit, Nanopower, 4-Wire TOUCH SCREEN CONTROLLER with I2C⑩ Interface |

| TSC2004_12 | 制造商:BB 制造商全稱:BB 功能描述:1.2V to 3.6V, 12-Bit, Nanopower, 4-Wire |

| TSC2004EVM | 功能描述:觸摸傳感器開發(fā)工具 TSC2004EVM Eval Mod RoHS:否 制造商:Cypress Semiconductor 工具用于評(píng)估: 接口類型: 工作電壓: 最大工作溫度: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。