- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383959 > TMC22153AKHC (FAIRCHILD SEMICONDUCTOR CORP) JT 32C 32#20 SKT PLUG PDF資料下載

參數(shù)資料

| 型號: | TMC22153AKHC |

| 廠商: | FAIRCHILD SEMICONDUCTOR CORP |

| 元件分類: | 顏色信號轉(zhuǎn)換 |

| 英文描述: | JT 32C 32#20 SKT PLUG |

| 中文描述: | COLOR SIGNAL DECODER, PQFP100 |

| 封裝: | MQFP-100 |

| 文件頁數(shù): | 66/84頁 |

| 文件大小: | 417K |

| 代理商: | TMC22153AKHC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁當(dāng)前第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁

TMC22x5yA

PRODUCT SPECIFICATION

66

REV. 1.0.0 2/4/03

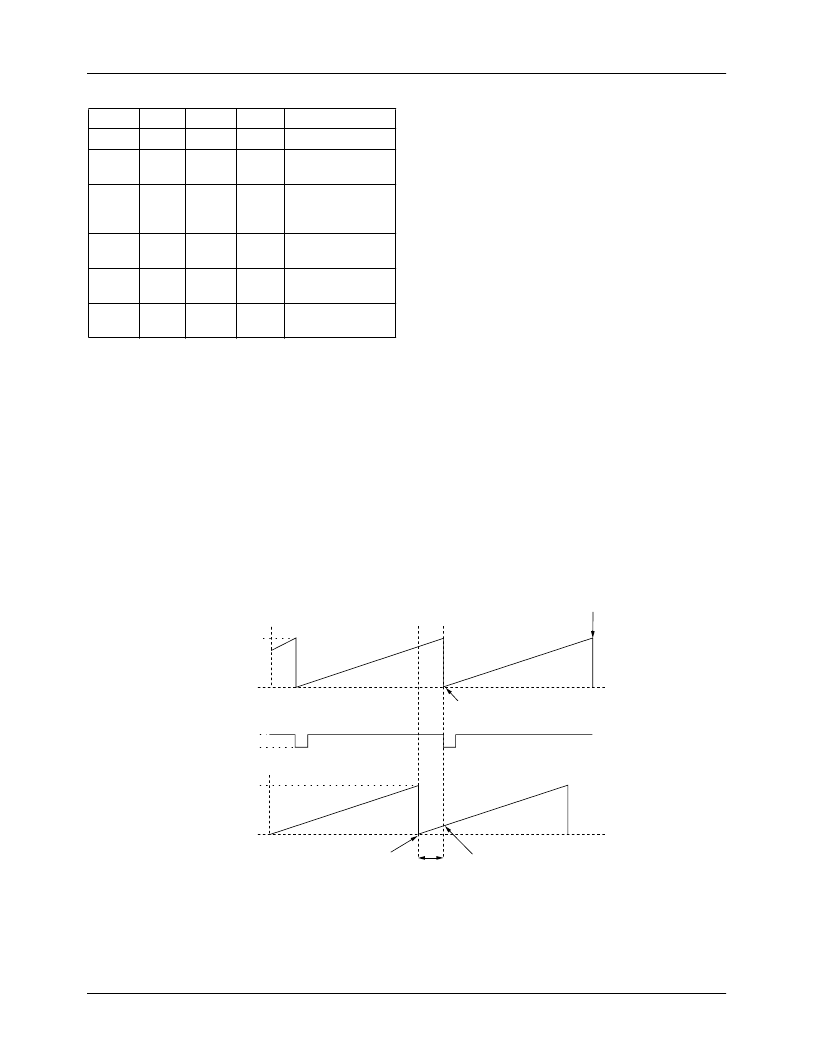

Table 23. Pixel Grab Control

If a single pixel every 4 fields in NTSC and 8 fields in PAL is

required to be grabbed, PGG and PGEN in register 30h

should be set HIGH. The pixel grab signal is the logical

AND of the GRABP, GRABL, and GRABF signals. GRABP

goes HIGH whenever the pixel count equals the programmed

pixel grab number, GRABL goes HIGH for one line when-

ever the line count equals the programmed line number,

and the GRABF goes HIGH for a field whenever the field

number equals the programmed field count.

If the same pixel on every line is required to be grabbed, then

PGG should be set LOW, which internally forces GRABL

and GRABF to be forced HIGH enabling the pixel grab

whenever GRABP goes HIGH.

The SET pin can be used to provide an external grab signal

when PGEXT is set HIGH in register 30h and the SET

function in register 00h, SET[2:0] is programmed to 110

(binary). In this mode the falling edge on the SET pin

triggers the pixel grab.

The GRABP, GRABL, and GRABF signals are available on

bits 0,1, and 2 respectively of the read only register 41. An

example of the pixel grab feature, would be grabbing a pixel

in the center of the burst period allowing the user to check

the burst height by reading the magnitude of the demodu-

lated U and V components. This would then allow the user to

compensate for any chrominance gain errors in the output

matrix.

The pixel grab value is delayed by 29 pixels from the pixel

count. This is the delay for all the pixel grab registers. Figure

33 shows this delay relative to GHSYNC. This means that if

29 is placed in the PG value, the actual pixel grabbed is

pixel 0.

The top two bits of the PG value provide the quadrant and

the bottom 9 bits provide the offset within that quadrant.

The integer part of STS/4 gives the maximum count for each

quadrant while the fractional result (bottom two bits)

provides the 0,1,2, or 3 count offset for the last quadrant.

For pixels value <= 4*Int(STS/4)

PG[10:9] = quadrant number

PG[8:0] = max quadrant count - Int(STS/4) + pixel offset

For pixels value > 4*Int(STS/4)

The quadrant is always number 3, ie PG[10:9] = 11 while the

pixel in excess of 4*Int(STS/4) is added to 1536.

LGEXT PGEN PGEXT LGEN

0

0

0

1

GRABS signal

GRABS = 0

GRABS =

PGRAB

GRABS = FGRAB

& LGRAB &

PGRAB

GRABS = NOT

(SET pin)

GRABS =

PGRAB

GRABS = NOT

(SET pin)

x

0

x

0

0

1

0

1

0

1

1

x

1

x

0

x

1

x

1

x

Figure 33. Relationship Between Pixel Count and Pixel Grab Value

STS-1

Pixel STS-1

Pixel 0

Pixel Grab

value 28

29 pixels

Pixel Grab

value 0

Pixel Count

Pixel Grab

GHSYNC

0

1

0

STS-1

0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TMC3003R2C80 | Triple Video D/A Converter |

| TMC3003KRC30 | Triple Video D/A Converter |

| TMC3003KRC50 | Triple Video D/A Converter |

| TMC3003KRC80 | Triple Video D/A Converter |

| TMC3003 | Triple Video D/A Converter |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TMC22191 | 制造商:CADEKA 制造商全稱:CADEKA 功能描述:Digital Video Encoders/Layering Engine |

| TMC22191KHC | 功能描述:視頻 IC D/V Encoder Layering Engine RoHS:否 制造商:Fairchild Semiconductor 工作電源電壓:5 V 電源電流:80 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-28 封裝:Reel |

| TMC22191R0C | 功能描述:視頻 IC D/V Encoder Layering Engine RoHS:否 制造商:Fairchild Semiconductor 工作電源電壓:5 V 電源電流:80 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-28 封裝:Reel |

| TMC22191R0CT | 功能描述:視頻 IC D/V Encoder Layering Engine RoHS:否 制造商:Fairchild Semiconductor 工作電源電壓:5 V 電源電流:80 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-28 封裝:Reel |

| TMC222 | 制造商:Trinamic 功能描述:IC SM WITH I2C INTERFACE |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。