- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383959 > TMC22153AKHC (FAIRCHILD SEMICONDUCTOR CORP) JT 32C 32#20 SKT PLUG PDF資料下載

參數(shù)資料

| 型號: | TMC22153AKHC |

| 廠商: | FAIRCHILD SEMICONDUCTOR CORP |

| 元件分類: | 顏色信號轉(zhuǎn)換 |

| 英文描述: | JT 32C 32#20 SKT PLUG |

| 中文描述: | COLOR SIGNAL DECODER, PQFP100 |

| 封裝: | MQFP-100 |

| 文件頁數(shù): | 57/84頁 |

| 文件大小: | 417K |

| 代理商: | TMC22153AKHC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁當前第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁

PRODUCT SPECIFICATION

TMC22x5yA

REV. 1.0.0 2/4/03

57

Y Offset

The 8 bit Y offset adds any offset required in the Y or RGB

data outputs. For example 64 (16) for the 64 (16) to 940

(235) 10 bit (8 bit) 601 outputs. When the output is YC

B

C

R

this offset is applied to the luminance data only. The Y offset

also provides the blanking level for RGB

outputs with syncs.

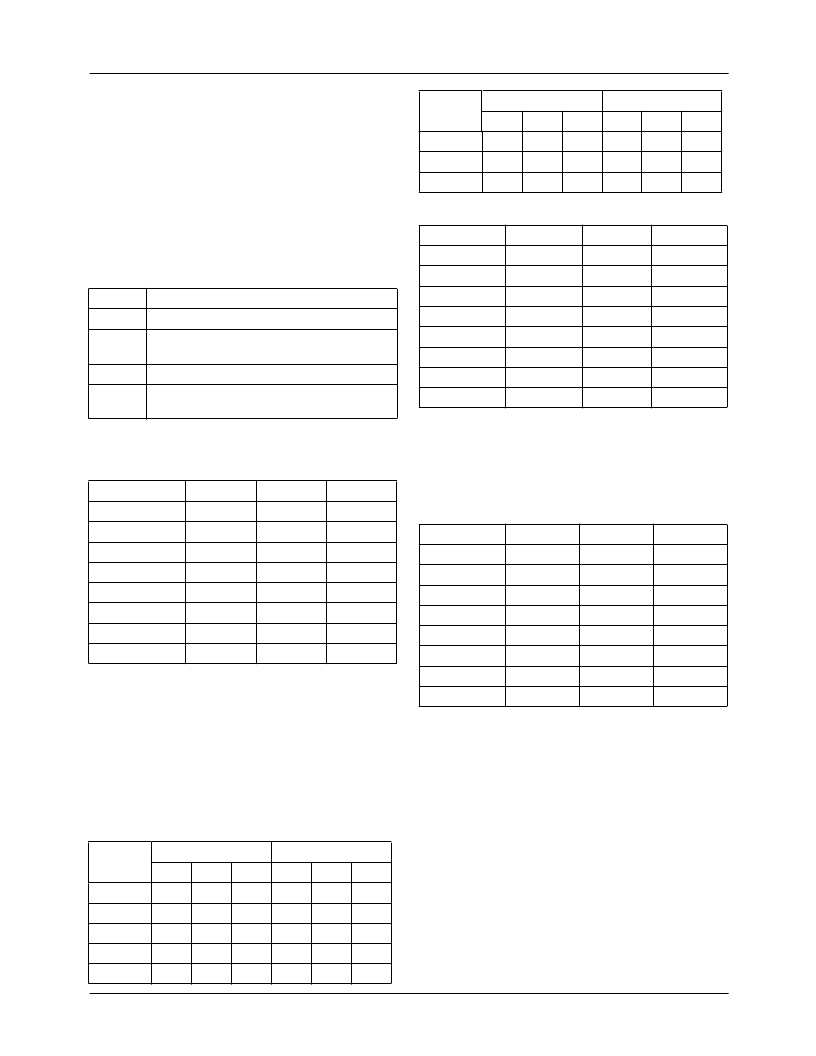

Matrix Limiters

The different limiters are listed below, 10 bit data is

assumed.

Table 13. Matrix Limiters

Examples of Output Matrix Operation

From the SMPTE-170M specification:

YC

B

C

R

data ranges are:

Y data range is 64 to 940 (876)

C

B

C

R

data ranges are 64 to 960 (+/- 448)

Matrix programming:

YGx = (876 / 540) = 1 + (159/256)

UGx = (448 / 236) = 1 + (230/256)

VGx = (448 / 332) = 1 + (89/256)

YOFF = 64

PED = 44

PAL digital composite input and RGB (0-1023) outputs:

The nominal scaling factors are simply:

YGx = 1023/572 = 1 + (202/256)

UGx = (1023/572)*(1/0.492) = 3 + (163/256)

VGx = (1023/572)*(1/0.877) = 2 + (10/256)

YOFF= 0

PED = 0

It is also possible with the architecture supplied to use the

limiters on the output of the matrix to clip the output video

deliberately by using a slightly larger gain than is required.

The Y_Offset can achieve the same by setting its value to be

one lsb less than the minimum clip level.

Buffer Registers

The BUFFER pin allows the user to externally switch

between two sets of internal registers that have the same

function. This register buffering allows the matrix gain,

picture hue, and luma offset to be changed at a known time

relative to the input data.

Registers 17 to 1D are selected when the BUFFER pin is

LOW and registers 27 to 2D are selected when the BUFFER

pin is HIGH. If the msb of the decoder product code DPC

2

is

LOW, an 8 bit decoder has been selected and the bottom 2

bits of registers 17 to 1A and 27 to 2A are forced to zero.

LMT

1-0

00

01

Comments

RGB output format, limited from 0 to 1023

YC

B

C

R

output format, Y limited from 0 to

1023 and C

B

C

R

limited to +/- 511.

RGB output format, limited from 64 to 940

YC

B

C

R

output format, Y limited from 64 to

940 and C

B

C

R

limited to +/- 448

10

11

Color

White

Yellow

Cyan

Green

Magenta

Red

Blue

Black

Y

U

0

V

0

54

-332

-278

278

332

-54

0

584

523

423

361

267

205

105

44

-236

79

-156

156

-79

236

0

Decoder Output

Y

C

B

939

0

841

-448

678

150

578

-296

426

296

CCIR 601 Spec

Y

C

B

940

0

840

-448

678

151

578

-296

426

296

Color

White

Yellow

Cyan

Green

Magenta

C

R

0

73

-447

-376

376

C

R

0

72

-448

-375

375

Red

Blue

Black

325

163

64

-150

448

0

447

-73

0

326

164

64

-151

448

0

448

-72

0

Color

White

Yellow

Cyan

Green

Magenta

Red

Blue

Black

Y

U

0

V

0

57

-352

-295

295

352

-57

0

572

507

401

336

236

171

65

0

-250

84

-165

165

-84

250

0

Color

White

Yellow

Cyan

Green

Magenta

Red

Blue

Black

G

R

B

1023

1023

1023

1023

0

0

0

0

1023

1023

0

0

1023

1023

0

0

1023

0

1023

1

1022

1

1023

0

Decoder Output

Y

C

B

CCIR 601 Spec

Y

C

B

Color

C

R

C

R

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TMC3003R2C80 | Triple Video D/A Converter |

| TMC3003KRC30 | Triple Video D/A Converter |

| TMC3003KRC50 | Triple Video D/A Converter |

| TMC3003KRC80 | Triple Video D/A Converter |

| TMC3003 | Triple Video D/A Converter |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TMC22191 | 制造商:CADEKA 制造商全稱:CADEKA 功能描述:Digital Video Encoders/Layering Engine |

| TMC22191KHC | 功能描述:視頻 IC D/V Encoder Layering Engine RoHS:否 制造商:Fairchild Semiconductor 工作電源電壓:5 V 電源電流:80 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-28 封裝:Reel |

| TMC22191R0C | 功能描述:視頻 IC D/V Encoder Layering Engine RoHS:否 制造商:Fairchild Semiconductor 工作電源電壓:5 V 電源電流:80 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-28 封裝:Reel |

| TMC22191R0CT | 功能描述:視頻 IC D/V Encoder Layering Engine RoHS:否 制造商:Fairchild Semiconductor 工作電源電壓:5 V 電源電流:80 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-28 封裝:Reel |

| TMC222 | 制造商:Trinamic 功能描述:IC SM WITH I2C INTERFACE |

發(fā)布緊急采購,3分鐘左右您將得到回復。