- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383957 > TLV320AIC3106IGQER (Texas Instruments, Inc.) LOW-POWER STEREO AUDIO CODEC FOR PORTABLE AUDIO/TELEPHONY PDF資料下載

參數(shù)資料

| 型號(hào): | TLV320AIC3106IGQER |

| 廠商: | Texas Instruments, Inc. |

| 元件分類: | Codec |

| 英文描述: | LOW-POWER STEREO AUDIO CODEC FOR PORTABLE AUDIO/TELEPHONY |

| 中文描述: | 低功耗立體聲音頻編解碼器的便攜式音頻/電話 |

| 文件頁(yè)數(shù): | 32/102頁(yè) |

| 文件大小: | 1259K |

| 代理商: | TLV320AIC3106IGQER |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)當(dāng)前第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)

www.ti.com

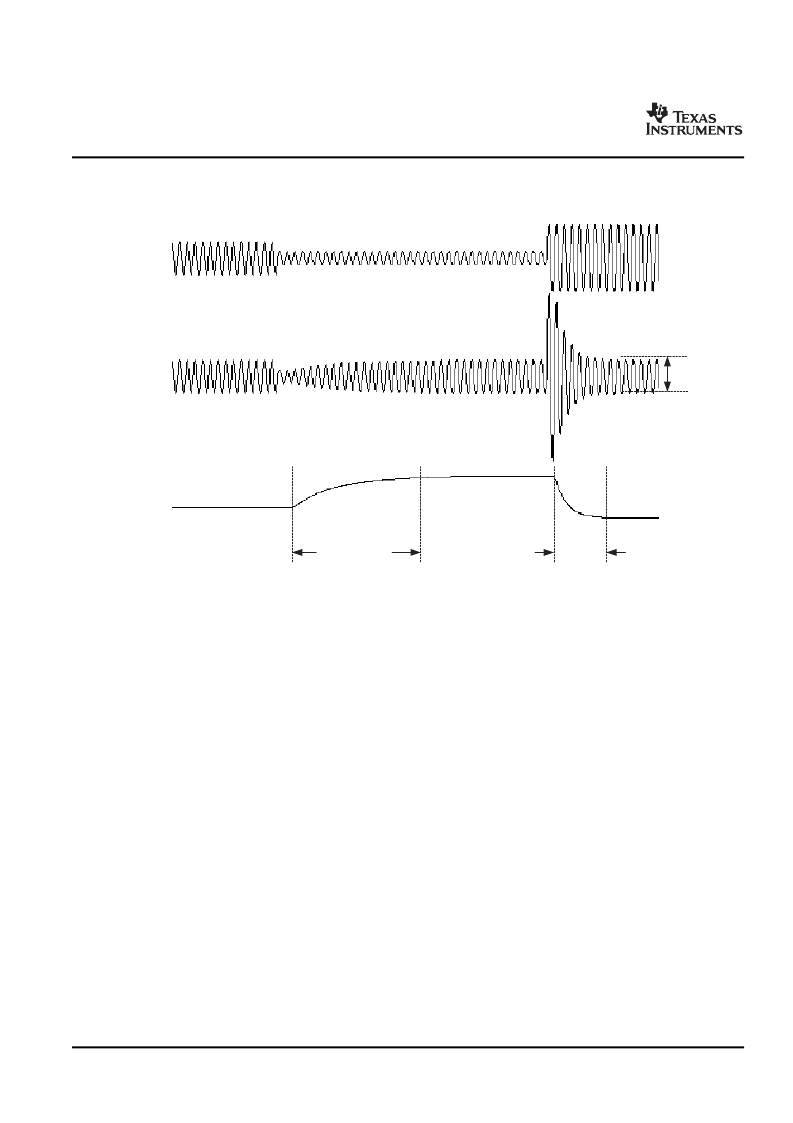

Decay Time

Target

Level

Input

Signal

Output

Signal

AGC

Gain

Attack

Time

STEREO AUDIO DAC

The TLV320AIC3106 includes a stereo audio DAC supporting sampling rates from 8 kHz to 96 kHz. Each

channel of the stereo audio DAC consists of a digital audio processing block, a digital interpolation filter, multi-bit

digital delta-sigma modulator, and an analog reconstruction filter. The DAC is designed to provide enhanced

performance at low sampling rates through increased oversampling and image filtering, thereby keeping

quantization noise generated within the delta-sigma modulator and signal images strongly suppressed within the

audio band to beyond 20 kHz. This is realized by keeping the upsampled rate constant at 128

×

Fsref and

changing the oversampling ratio as the input sample rate is changed. For an Fsref of 48 kHz, the digital

delta-sigma modulator always operates at a rate of 6.144 MHz. This ensures that quantization noise generated

within the delta-sigma modulator stays low within the frequency band below 20 kHz at all sample rates. Similarly,

for an Fsref rate of 44.1 kHz, the digital delta-sigma modulator always operates at a rate of 5.6448 MHz.

TLV320AIC3106

SLAS509B–DECEMBER 2006–REVISED JUNE 2007

Maximum PGA gain applicable

allows the user to restrict the maximum PGA gain that can be applied by the

AGC algorithm. This can be used for limiting PGA gain in situations where environmental noise is greater than

programmed noise threshold. It can be programmed from 0 dB to +59.5 dB in steps of 0.5 dB.

Figure 27. Typical Operation of the AGC Algorithm During Speech Recording

Note that the time constants here are correct when the ADC is not in double-rate audio mode. The time

constants are achieved using the Fsref value programmed in the control registers. However, if the Fsref is set in

the registers to, for example, 48 kHz, but the actual audio clock or PLL programming actually results in a

different Fsref in practice, then the time constants would not be correct.

The actual AGC decay time maximum is based on a counter length, so the maximum decay time scales with the

clock set up that is used.

Table 1

shows the relationship of the NADC ratio to the maximum time available for

the AGC decay. In practice, these maximum times are extremely long for audio applications and should not limit

any practical AGC decay time that is needed by the system.

The following restrictions apply in the case when the PLL is powered down and double-rate audio mode is

enabled in the DAC.

Allowed Q values = 4, 8, 9, 12, 16

Q values where equivalent Fsref can be achieved by turning on PLL

Q = 5, 6, 7 (set P = 5 / 6 / 7 and K = 16.0 and PLL enabled)

Q = 10, 14 (set P = 5, 7 and K = 8.0 and PLL enabled)

32

Submit Documentation Feedback

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TLV341_07 | LOW-VOLTAGE RAIL-TO-RAIL OUTPUT CMOS OPERATIONAL AMPLIFLERS WITH SHUTDOWN |

| TLV431ACDBV | LOW-VOLTAGE ADJUSTABLE PRECISION SHUNT REGULATORS |

| TLV431ID | LOW-VOLTAGE ADJUSTABLE PRECISION SHUNT REGULATORS |

| TLV431AIDBV | LOW-VOLTAGE ADJUSTABLE PRECISION SHUNT REGULATORS |

| TLV431ASNT1 | MS/STANDARD CYLINDRICAL MIL-C-5015 SERIES 3102A SOLID SHELL BOX MOUNT RECEPTACLES, STRAIGHT BODY STYLE, SOLDER TERMINATION, 14S SHELL SIZE, 14S-6 INSERT ARRANGEMENT, RECEPTACLE GENDER, 6 CONTACTS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TLV320AIC3106IRGZR | 功能描述:接口—CODEC Lo-Pwr Stereo CODEC RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉(zhuǎn)換速率:48 kSPs 接口類型:I2C ADC 數(shù)量:2 DAC 數(shù)量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

| TLV320AIC3106IRGZT | 功能描述:接口—CODEC Lo-Pwr Stereo CODEC RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉(zhuǎn)換速率:48 kSPs 接口類型:I2C ADC 數(shù)量:2 DAC 數(shù)量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

| TLV320AIC3106IZQE | 功能描述:接口—CODEC Low-Power Stereo RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉(zhuǎn)換速率:48 kSPs 接口類型:I2C ADC 數(shù)量:2 DAC 數(shù)量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

| TLV320AIC3106IZQER | 功能描述:接口—CODEC Low-Power Stereo RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉(zhuǎn)換速率:48 kSPs 接口類型:I2C ADC 數(shù)量:2 DAC 數(shù)量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

| TLV320AIC3107 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:LOW-POWER STEREO CODEC WITH INTEGRATED MONO CLASS-D SPEAKER AMPLIFIER |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。