- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383844 > STPCD01 STPC CLIENT DATASHEET / PC COMPATIBLE EMBEDED MICROPROCESSOR PDF資料下載

參數(shù)資料

| 型號: | STPCD01 |

| 英文描述: | STPC CLIENT DATASHEET / PC COMPATIBLE EMBEDED MICROPROCESSOR |

| 中文描述: | STPC客戶部件/ PC兼容的嵌入式微處理器 |

| 文件頁數(shù): | 43/61頁 |

| 文件大小: | 1007K |

| 代理商: | STPCD01 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁當(dāng)前第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁

ELECTRICAL SPECIFICATIONS

Issue 2.2 - October 13, 2000

43/61

10e

4

11

4

SA[19:0] & SBHE valid before IOR#, IOW# asserted

XTALO to IOW# valid

11a

4

Memory access to 16 bit ISA Slave - 2BCLK

11b

4

Memory access to 16 bit ISA Slave - Standard 3BCLK

11c

4

Memory access to 16 bit ISA Slave - 4BCLK

11d

4

Memory access to 8 bit ISA Slave - 2BCLK

Memory access to 8 bit ISA Slave - Standard 3BCLK

ALE# asserted before ALE# negated

ALE# asserted before MEMR#, MEMW# asserted

13a

4

Memory Access to 16 bit ISA Slave

13b

4

Memory Access to 8 bit ISA Slave

ALE# asserted before SMEMR#, SMEMW# asserted

13c

4

Memory Access to 16 bit ISA Slave

13d

4

Memory Access to 8 bit ISA Slave

ALE# asserted before IOR#, IOW# asserted

ALE# asserted before AL[23:17]

14a

4

Non compressed

14b

4

Compressed

ALE# asserted before MEMR#, MEMW#, SMEMR#, SMEMW# negated

15a

4

Memory Access to 16 bit ISA Slave- 4 BCLK

15e

4

Memory Access to 8 bit ISA Slave- Standard Cycle

ALE# negated before LA[23:17] invalid (non compressed)

ALE# negated before LA[23:17] invalid (compressed)

MEMR#, MEMW# asserted before LA[23:17]

22a

4

Memory access to 16 bit ISA Slave.

22b

4

Memory access to 8 bit ISA Slave.

MEMR#, MEMW# asserted before MEMR#, MEMW# negated

23b

4

Memory access to 16 bit ISA Slave Standard cycle

23e

4

Memory access to 8 bit ISA Slave Standard cycle

SMEMR#, SMEMW# asserted before SMEMR#, SMEMW# negated

23h

4

Memory access to 16 bit ISA Slave Standard cycle

23l

4

Memory access to 16 bit ISA Slave Standard cycle

IOR#, IOW# asserted before IOR#, IOW# negated

23o

4

Memory access to 16 bit ISA Slave Standard cycle

23r

4

Memory access to 8 bit ISA Slave Standard cycle

MEMR#, MEMW# asserted before SA[19:0]

24b

4

Memory access to 16 bit ISA Slave Standard cycle

24d

4

Memory access to 8 bit ISA Slave - 3BLCK

24e

4

Memory access to 8 bit ISA Slave Standard cycle

24f

4

Memory access to 8 bit ISA Slave - 7BCLK

SMEMR#, SMEMW# asserted before SA[19:0]

24h Memory access to 16 bit ISA Slave Standard cycle

24i

4

Memory access to 16 bit ISA Slave - 4BCLK

24k

4

Memory access to 8 bit ISA Slave - 3BCLK

24l

4

Memory access to 8 bit ISA Slave Standard cycle

Note; The signal numbering refers to

Table 4-10

Note 4; These timings are extracted from simulations and are not garanteed by testing

2T

Cycles

2T

2T

2T

2T

2T

1T

Cycles

Cycles

Cycles

Cycles

Cycles

Cycles

11e

4

12

4

13

4

2T

2T

Cycles

Cycles

13

4

2T

2T

2T

Cycles

Cycles

Cycles

13e

4

14

4

15T

15T

Cycles

Cycles

15

4

11T

11T

14T

14T

Cycles

Cycles

Cycles

Cycles

18a

4

18a

4

22

4

13T

13T

Cycles

Cycles

23

4

9T

9T

Cycles

Cycles

23

4

9T

9T

Cycles

Cycles

23

4

9T

9T

Cycles

Cycles

24

4

10T

10T

10T

10T

Cycles

Cycles

Cycles

Cycles

24

4

10T

10T

10T

10T

Cycles

Cycles

Cycles

Cycles

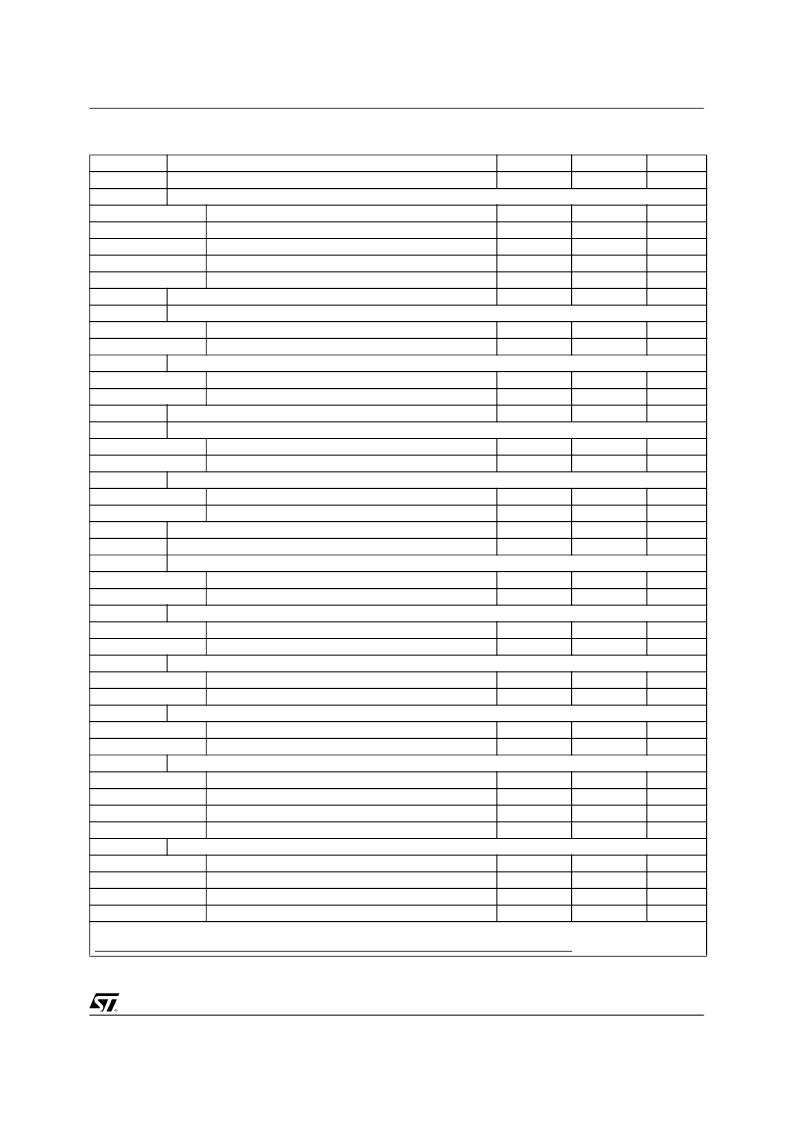

Table 4-8. ISA Bus AC Timing

Name

Parameter

Min

Max

Units

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| STPCD0110BTC3 | 32-Bit Microprocessor |

| STPCD0112BTC3 | 32-Bit Microprocessor |

| STPCD0113BTC3 | 32-Bit Microprocessor |

| STPCI01 | STPC INDUSTRIAL / PC COMPATIBLE EMBEDED MICROPROCESSOR |

| STPCI2 | STPC ATLAS DATASHEET / X86 CORE PC COMPATIBLE SYSTEM-ON-CHIP FOR TERMINALS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| STPCD0110BTC3 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:32-Bit Microprocessor |

| STPCD0112BTC3 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:32-Bit Microprocessor |

| STPCD0113BTC3 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:32-Bit Microprocessor |

| STPCD0166BTA3 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:PC Compatible Embedded Microprocessor |

| STPCD0166BTC3 | 制造商:STMicroelectronics 功能描述:MPU STPC RISC 64-Bit 66MHz 388-Pin BGA |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。