- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385871 > ST70135A (意法半導(dǎo)體) ASCOTTM DMT TRANSCEIVER PDF資料下載

參數(shù)資料

| 型號: | ST70135A |

| 廠商: | 意法半導(dǎo)體 |

| 英文描述: | ASCOTTM DMT TRANSCEIVER |

| 中文描述: | ASCOTTM大唐收發(fā)器 |

| 文件頁數(shù): | 17/29頁 |

| 文件大小: | 198K |

| 代理商: | ST70135A |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁當(dāng)前第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁

ST70135A

17/29

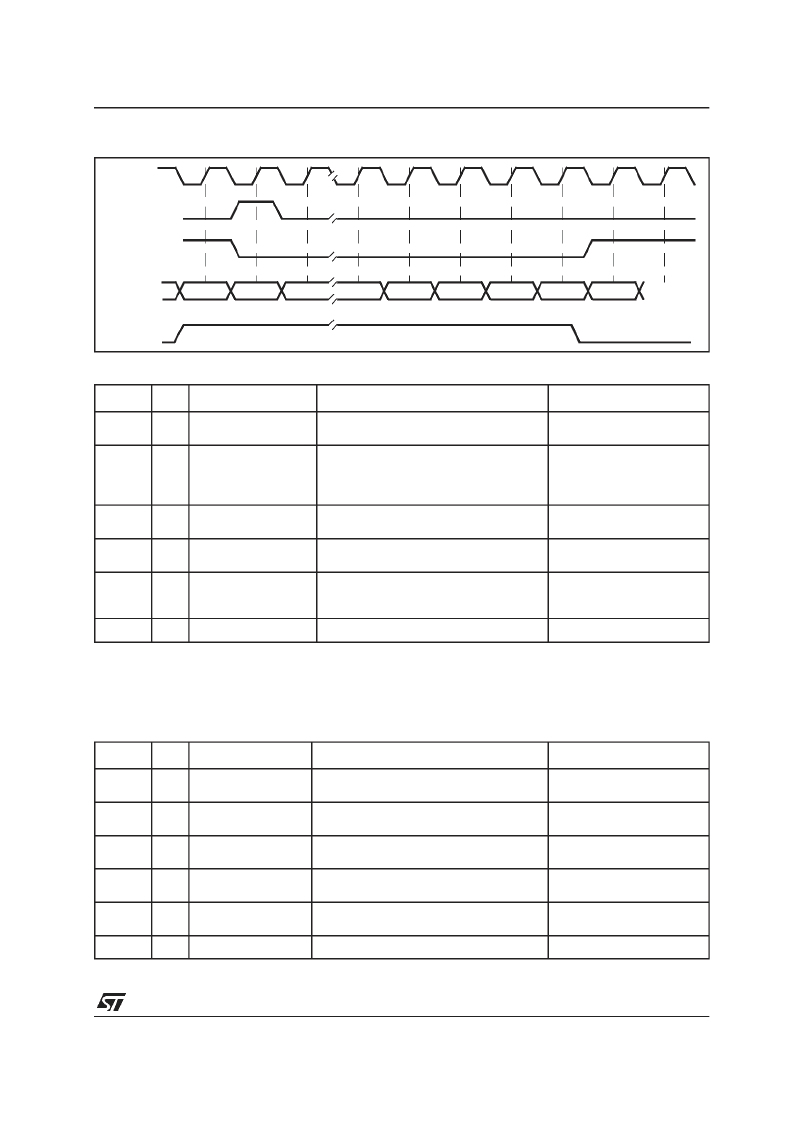

Figure 14 :

Timing (Utopia 1 Receive Interface)

Pin Description

Note

When RxEnb is asserted, the ST70135A reads data from its internal fifo and presents it on RxData and

RxSOC oneach low-to-hightransition of RxClk, ie theATM layer chip samples all RxData and RxSOC on

the rising edge of RxSOC on the rising edge of RxClk.

1. Active low signal

Pin Description

Note

1. Active low signal

Name

Type

Meaning

Usage

Remark

RxClav

O

Receive Cell available

Signals to the ATM chip that the ST70135A

has a cell ready for transfer

Remains active for the entire

cell transfer

RxEnb

1

I

Receive Enable

Signals to the ST70135A that the ATM chip

will sample and accept data during next

clock cycle

RxData and RxSOC could be

tri-state when RxEnb* is

inactive (high). Active low

signal

RxClk

I

Receive Byte Clock

Gives the timing signal for the transfer,

generated by ATM layer chip.

RxData

O

Receive Data (8bits)

ATM cell data, from ST70135A chip to ATM

chip, byte wide. Rx Data [7] is the MSB.

RxSOC

O

Receive Start Cell

Identifies the cell boundary on RxData

Indicate to the ATM layer

chip that RxData contains

the first valid byte of a cell.

RxRef

1

O

Reference Clock

8 kHz clock transported over the network

Active low signal

Name

Type

Meaning

Usage

Remark

TxClav

O

Transmit Cell

available

Signals to the ATM chip that the physical

layer chip is ready to accept a complete cell

Remains active for the entire

cell transfer

TxEnb

1

I

Transmit Enable

Signals to the ST70135A that TxData and

TxSOC are valid

TxClk

I

Transmit Byte Clock

Gives the timing signal for the transfer,

generated by ATM layer chip.

TxData

I

Transmit Data (8bits)

ATMcell data, from ATM layerchip to

ST70135A, byte wide. TxData [7] is theMSB.

TxSOC

I

Transmit Start of Cell

Identifies the cell boundary on TxData

TxData contains the first

valid byte of the cell.

TxRef

1

I

Reference Clock

8kHz clock from the ATMlayer chip

RxCLK

RxSOC

RxENB

X

H1

H2

P44

P45

P47

P48

X

P46

RxDATA

RxCLAV

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ST70136 | CPE ADSL ANALOG FRONT END |

| ST70136B | CPE ADSL ANALOG FRONT END |

| ST70136G | CPE ADSL ANALOG FRONT END |

| ST70137 | UNICORNTM PCI & USB CONTROLLERLESS ADSL DMT TRANSCEIVER |

| ST70137TQFP | UNICORNTM PCI & USB CONTROLLERLESS ADSL DMT TRANSCEIVER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ST70136 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:CPE ADSL ANALOG FRONT END |

| ST70136B | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:CPE ADSL ANALOG FRONT END |

| ST70136G | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:CPE ADSL ANALOG FRONT END |

| ST70136Q | 功能描述:射頻無線雜項 ADSL Analg Front-End RoHS:否 制造商:Texas Instruments 工作頻率:112 kHz to 205 kHz 電源電壓-最大:3.6 V 電源電壓-最小:3 V 電源電流:8 mA 最大功率耗散: 工作溫度范圍:- 40 C to + 110 C 封裝 / 箱體:VQFN-48 封裝:Reel |

| ST70137 | 制造商:STMicroelectronics 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。