- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄383837 > ST16C580 (Exar Corporation) UART WITH 16-BYTE FIFO’s AND INFRARED (IrDA) ENCODER/DECODER PDF資料下載

參數(shù)資料

| 型號(hào): | ST16C580 |

| 廠(chǎng)商: | Exar Corporation |

| 英文描述: | UART WITH 16-BYTE FIFO’s AND INFRARED (IrDA) ENCODER/DECODER |

| 中文描述: | UART的16字節(jié)FIFO的和紅外線(xiàn)(IrDA)編碼/解碼器 |

| 文件頁(yè)數(shù): | 25/41頁(yè) |

| 文件大?。?/td> | 244K |

| 代理商: | ST16C580 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)當(dāng)前第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)

ST16C580

25

Rev. 1.20

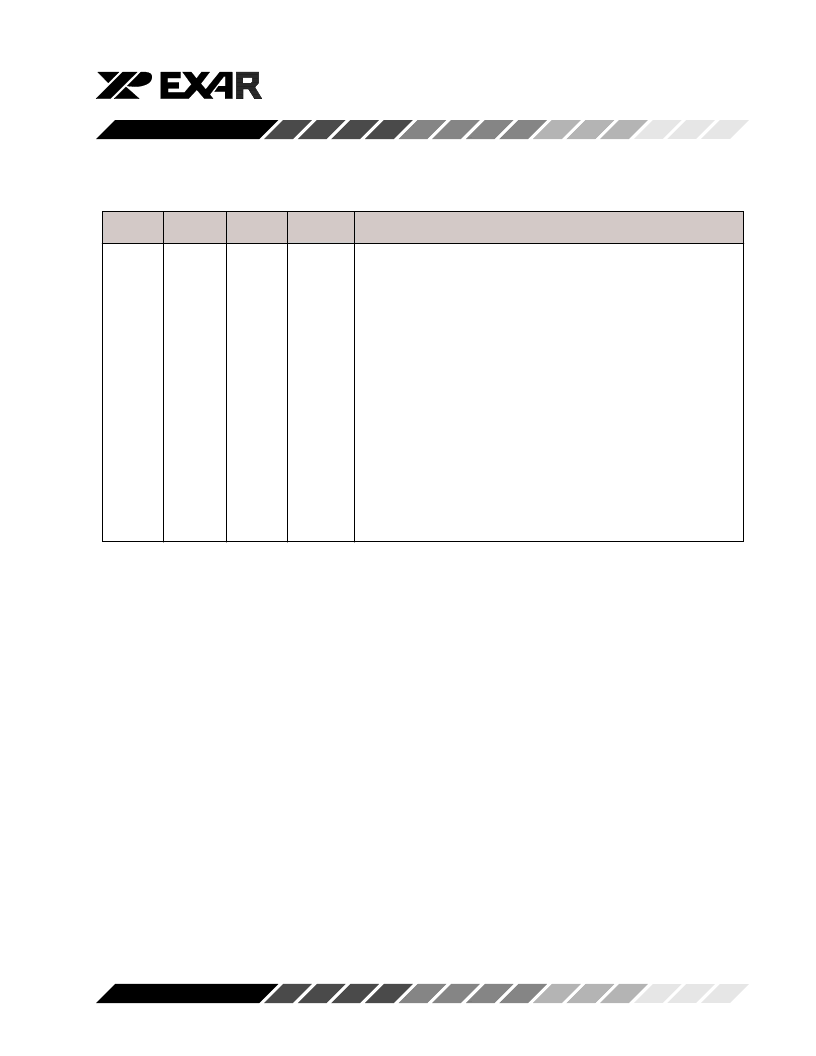

Table 7, SOFTWARE FLOW CONTROL FUNCTIONS

Cont-3

Cont-2

Cont-1

Cont-0

TX, RX software flow controls

0

1

0

1

X

X

X

1

0

0

1

1

X

X

X

0

X

X

X

X

0

1

0

1

X

X

X

X

0

0

1

1

No transmit flow control

Transmit Xon1/Xoff1

Transmit Xon2/Xoff2

Transmit Xon1 and Xon2/Xoff1 and Xoff2

No receive flow control

Receiver compares Xon1/Xoff1

Receiver compares Xon2/Xoff2

Transmit Xon1/ Xoff1.

Receiver compares Xon1 and Xon2,

Xoff1 and Xoff2

Transmit Xon2/Xoff2

Receiver compares Xon1 and Xon2/Xoff1 and Xoff2

Transmit Xon1 and Xon2/Xoff1 and Xoff2

Receiver compares Xon1 and Xon2/Xoff1 and Xoff2

No transmit flow control

Receiver compares Xon1 and Xon2/Xoff1 and Xoff2

0

1

1

1

1

1

1

1

0

0

1

1

EFR BIT-4:

Enhanced function control bit. The content of the IER

bits 4-7, ISR bits 4-5, FCR bits 4-5, and MCR bits 5-7

can be modified and latched. After modifying any bits

in the enhanced registers, EFR bit-4 can be set to a

logic 0 to latch the new values. This feature prevents

existing software from altering or overwriting the 580

enhanced functions.

Logic 0 = disable/latch enhanced features. IER bits 4-

7, ISR bits 4-5, FCR bits 4-5, and MCR bits 5-7 are

saved to retain the user settings, then IER bits 4-7, ISR

bits 4-5, FCR bits 4-5, and MCR bits 5-7 are initialized

to the default values shown in the Internal Resister

Table. After a reset, the IER bits 4-7, ISR bits 4-5, FCR

bits 4-5, and MCR bits 5-7 are set to a logic 0 to be

compatible with ST16C550 mode. (normal default

condition).

Logic 1 = Enables the enhanced functions. When this

bit is set to a logic 1 all enhanced features of the 580

are enabled and user settings stored during a reset will

be restored.

EFR BIT-5:

Logic 0 = Special Character Detect Disabled (normal

default condition)

Logic 1 = Special Character Detect Enabled. The 580

compares each incoming receive character with Xoff-

2 data. If a match exists, the received data will be

transferred to FIFO and ISR bit-4 will be set to indicate

detection of special character. Bit-0 in the X-registers

corresponds with the LSB bit for the receive character.

When this feature is enabled, the normal software flow

control must be disabled (EFR bits 0-3 must be set to

a logic 0).

EFR BIT-6:

Automatic RTS may be used for hardware flow control

by enabling EFR bit-6. When AUTO RTS is selected,

an interrupt will be generated when the receive FIFO

is filled to the programmed trigger level and -RTS will

go to a logic 1 at the next trigger level. -RTS will return

to a logic 0 when data is unloaded below the next lower

trigger level (Programmed trigger level -1). The state

of this register bit changes with the status of the

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ST16C580CQ48 | UART WITH 16-BYTE FIFO’s AND INFRARED (IrDA) ENCODER/DECODER |

| ST16C580IJ44 | UART WITH 16-BYTE FIFO’s AND INFRARED (IrDA) ENCODER/DECODER |

| ST16C580IP40 | UART WITH 16-BYTE FIFO’s AND INFRARED (IrDA) ENCODER/DECODER |

| ST16C580IQ48 | UART WITH 16-BYTE FIFO’s AND INFRARED (IrDA) ENCODER/DECODER |

| ST16C580CP40 | Linear Voltage Regulator IC; Output Current Max:350mA; Supply Voltage Max:6V; Package/Case:8-TSSOP; Output Current:350mA; Output Voltage:3.3V; Current Rating:30.05A; Leaded Process Compatible:No; Output Voltage Max:3.3V |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ST16C580_05 | 制造商:EXAR 制造商全稱(chēng):EXAR 功能描述:UART WITH 16-BYTE FIFO’s AND INFRARED (IrDA) ENCODER/DECODER |

| ST16C580CJ44 | 制造商:EXAR 制造商全稱(chēng):EXAR 功能描述:UART WITH 16-BYTE FIFO’s AND INFRARED (IrDA) ENCODER/DECODER |

| ST16C580CP40 | 制造商:EXAR 制造商全稱(chēng):EXAR 功能描述:UART WITH 16-BYTE FIFO’s AND INFRARED (IrDA) ENCODER/DECODER |

| ST16C580CQ-0A-EVB | 功能描述:界面開(kāi)發(fā)工具 Supports C580 48 ld TQFP, ISA Interface RoHS:否 制造商:Bourns 產(chǎn)品:Evaluation Boards 類(lèi)型:RS-485 工具用于評(píng)估:ADM3485E 接口類(lèi)型:RS-485 工作電源電壓:3.3 V |

| ST16C580CQ48 | 制造商:Rochester Electronics LLC 功能描述: 制造商:Exar Corporation 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。