- 您現(xiàn)在的位置:買(mǎi)賣IC網(wǎng) > PDF目錄383837 > ST16C550 (Exar Corporation) UART with 16-Byte FIFO(通用異步接收器/發(fā)送器(帶16字節(jié)的先進(jìn)先出)) PDF資料下載

參數(shù)資料

| 型號(hào): | ST16C550 |

| 廠商: | Exar Corporation |

| 英文描述: | UART with 16-Byte FIFO(通用異步接收器/發(fā)送器(帶16字節(jié)的先進(jìn)先出)) |

| 中文描述: | 的UART具有16字節(jié)FIFO(通用異步接收器/發(fā)送器(帶16字節(jié)的先進(jìn)先出)) |

| 文件頁(yè)數(shù): | 17/36頁(yè) |

| 文件大?。?/td> | 235K |

| 代理商: | ST16C550 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)當(dāng)前第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)

ST16C550

17

Rev. 4.20

ISR BIT-0:

Logic 0 = An interrupt is pending and the ISR contents

may be used as a pointer to the appropriate interrupt

service routine.

Logic 1 = No interrupt pending. (normal default condi-

tion)

ISR BIT 1-3: (logic 0 or cleared is the default condition)

These bits indicate the source for a pending interrupt at

interrupt priority levels 1, 2, and 3 (See Interrupt Source

Table).

ISR BIT 4-5 Not used and set to “0”.

ISR BIT 6-7: (logic 0 or cleared is the default condition)

These bits are set to a logic 0 when the FIFO is not being

used. They are set to a logic 1 when the FIFO’s are

enabled

Line Control Register (LCR)

The Line Control Register is used to specify the

asynchronous data communication format. The word

length, the number of stop bits, and the parity are

selected by writing the appropriate bits in this register.

LCR BIT 0-1: (logic 0 or cleared is the default condi-

tion)

These two bits specify the word length to be transmit-

ted or received.

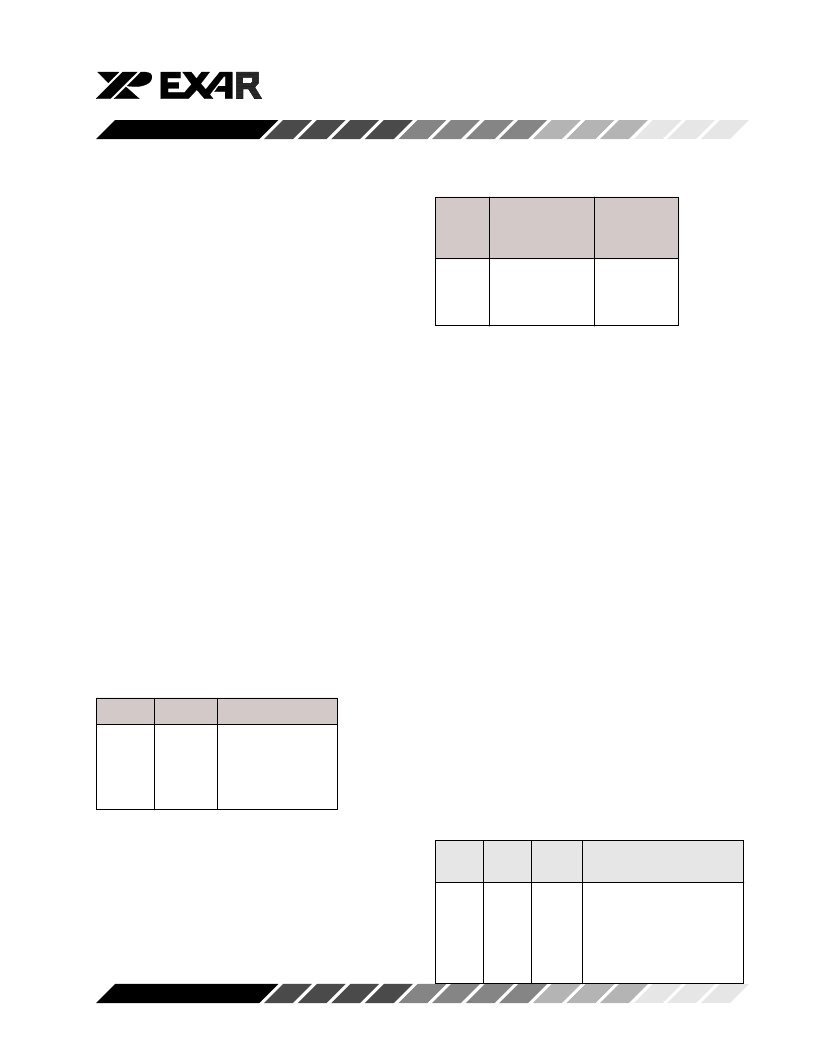

BIT-1

BIT-0

Word length

0

0

1

1

0

1

0

1

5

6

7

8

LCR BIT-2: (logic 0 or cleared is the default condition)

The length of stop bit is specified by this bit in

conjunction with the programmed word length.

BIT-2

Word length

Stop bit

length

(Bit time(s))

0

1

1

5,6,7,8

5

6,7,8

1

1-1/2

2

LCR BIT-3:

Parity or no parity can be selected via this bit.

Logic 0 = No parity (normal default condition)

Logic 1 = A parity bit is generated during the transmis-

sion, receiver checks the data and parity for transmis-

sion errors.

LCR BIT-4:

If the parity bit is enabled with LCR bit-3 set to a logic

1, LCR BIT-4 selects the even or odd parity format.

Logic 0 = ODD Parity is generated by forcing an odd

number of logic 1’s in the transmitted data. The

receiver must be programmed to check the same

format. (normal default condition)

Logic 1 = EVEN Parity

is generated by forcing an even

the number of logic 1’s in the transmitted. The receiver

must be programmed to check the same format.

LCR BIT-5:

If the parity bit is enabled, LCR BIT-5 selects the

forced parity format.

LCR BIT-5 = logic 0, parity is not forced (normal

default condition)

LCR BIT-5 = logic 1 and LCR BIT-4 = logic 0, parity bit

is forced to a logical 1 for the transmit and receive

data.

LCR BIT-5 = logic 1 and LCR BIT-4 = logic 1, parity bit

is forced to a logical 0 for the transmit and receive

data.

LCR

Bit-5

LCR

Bit-4

LCR

Bit-3

Parity selection

X

0

0

1

1

X

0

1

0

1

0

1

1

1

1

No parity

Odd parity

Even parity

Force parity “1”

Forced “0”

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ST16C552 | Dual UART with 16-Byte FIFO and Parallel Printer Port(雙通用異步接收器/發(fā)送器(帶16字節(jié)的先進(jìn)先出和并行打印機(jī)端口)) |

| ST16C552A | Dual UART with 16-Byte FIFO and Parallel Printer Port(雙通用異步接收器/發(fā)送器(帶16字節(jié)的先進(jìn)先出和并行打印機(jī)端口)) |

| ST16C554DCJ68 | QUAD UART WITH 16-BYTE FIFOS |

| ST68C554 | QUAD UART WITH 16-BYTE FIFOS |

| ST16C554DIJ68 | Plug-In Relay; Contacts:DPDT; Contact Carry Current:15A; Coil Voltage AC Max:120V; Relay Mounting:Plug-In; Relay Terminals:Quick Connect; Coil Resistance:4430ohm RoHS Compliant: Yes |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ST16C550_05 | 制造商:EXAR 制造商全稱:EXAR 功能描述:UART WITH 16-BYTE FIFO’s |

| ST16C550CJ44 | 制造商:Exar 功能描述:Bulk |

| ST16C550CJ44-F | 功能描述:UART 接口集成電路 2.97V-5.5V 16B FIFO temp 0C to 70C; UART RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| ST16C550CJ44TR-F | 功能描述:UART 接口集成電路 SNGL UART W/16BYTE FIFO RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| ST16C550CP40 | 功能描述:UART 接口集成電路 SINGLE UART W/16 BYTE FIFO RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。