- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385792 > S25FL001D0FNFI001 (SPANSION LLC) 2 Megabit, 1 Megabit CMOS 3.0 Volt Flash Memory with 25 MHz SPI Bus Interface PDF資料下載

參數(shù)資料

| 型號(hào): | S25FL001D0FNFI001 |

| 廠商: | SPANSION LLC |

| 元件分類: | DRAM |

| 英文描述: | 2 Megabit, 1 Megabit CMOS 3.0 Volt Flash Memory with 25 MHz SPI Bus Interface |

| 中文描述: | 1M X 1 SPI BUS SERIAL EEPROM, PDSO8 |

| 封裝: | 6 X 5 MM, LEAD FREE, WSON-8 |

| 文件頁數(shù): | 20/38頁 |

| 文件大小: | 488K |

| 代理商: | S25FL001D0FNFI001 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁當(dāng)前第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁

20

S25FL Family (Serial Peripheral Interface)

30167A+1 June 9, 2004

P r e l i m i n a r y I n f o r m a t i o n

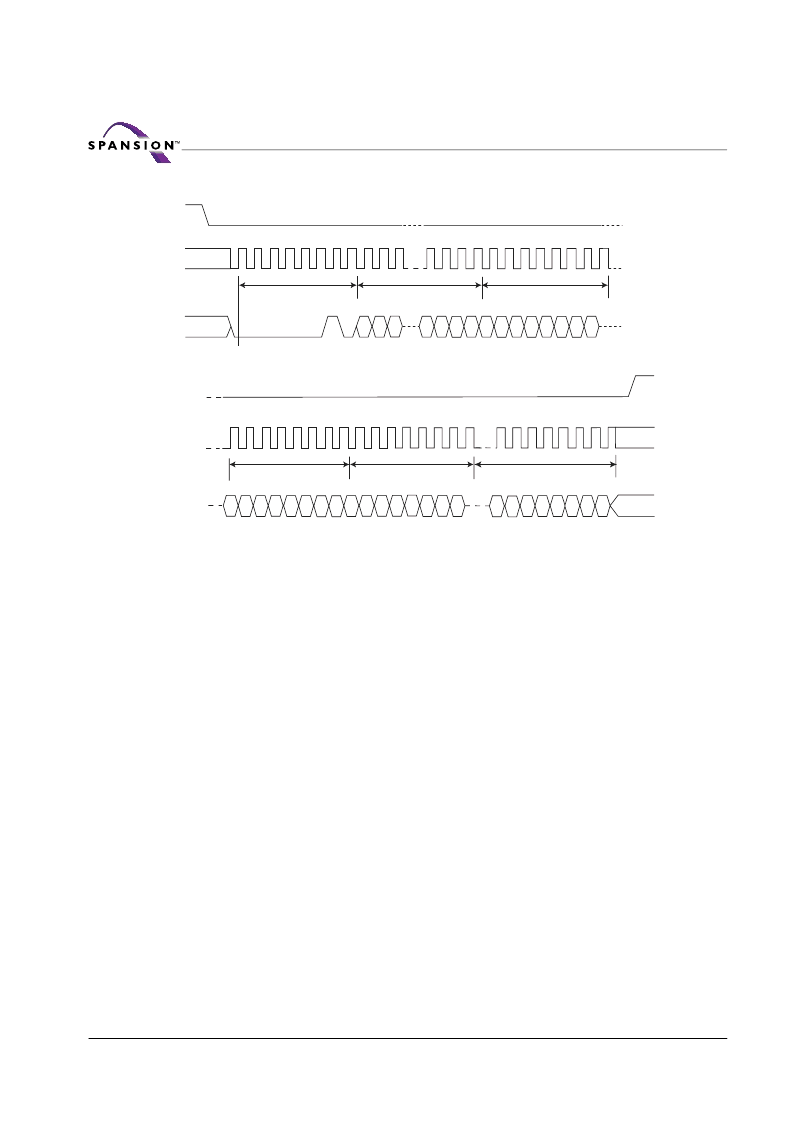

Figure 11. Page Program (PP) Instruction Sequence

Sector Erase (SE)

The Sector Erase (SE) instruction sets to 1 (FFh) all bits inside the chosen sector.

Before it can be accepted, a Write Enable (WREN) instruction must previously

have been executed. After the Write Enable (WREN) instruction has been de-

coded, the device sets the Write Enable Latch (WEL).

The Sector Erase (SE) instruction is entered by driving Chip Select (CS#) Low,

followed by the instruction code, and three address bytes on Serial Data Input

(SI). Any address inside the Sector (see Table

1

and Table

2

) is a valid address

for the Sector Erase (SE) instruction. Chip Select (CS#) must be driven Low for

the entire duration of the sequence.

The instruction sequence is shown in

Figure 12

.

Chip Select (CS#) must be driven High after the eighth bit of the last address byte

has been latched in, otherwise the Sector Erase (SE) instruction is not executed.

As soon as Chip Select (CS#) is driven High, the self-timed Sector Erase cycle

(whose duration is tSE) is initiated. While the Sector Erase cycle is in progress,

the Status Register may be read to check the value of the Write In Progress (WIP)

bit. The Write In Progress (WIP) bit is 1 during the self-timed Sector Erase cycle,

and is 0 when it is completed. At some unspecified time before the cycle is com-

pleted, the Write Enable Latch (WEL) bit is reset.

A Sector Erase (SE) instruction applied to any memory area that is protected by

the Block Protect (BP1, BP0) bits (see Table

1

and Table

2

) is not executed.

0

34

33

32

31

30

29

28

10

9

8

7

6

5

4

3

2

1

3536 3738 39

46

45

44

43

42

41

40

4748 4950 51 52 5354 55

2

2

2

2

2

2

2

2

23 22 21

3

2

1

0

7

6

5

4

3

2

1

0

Data Byte 1

24-Bit Address

Instruction

Data Byte 2

Data Byte 3

Data Byte 256

MSB

MSB

MSB

MSB

MSB

SCK

SI

SCK

SI

7

6

5

4

3

2

1

0

7

6

5

4

3

2

1

0

7

6

5

4

3

2

1

0

CS#

CS#

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| S25XXXH | SCR |

| S2516MH | SCR |

| S29GL032A30FFI012 | 64 Megabit, 32 Megabit, and 16 Megabit 3.0-Volt only Page Mode Flash Memory Featuring 200 nm MirrorBit Process Technology |

| S29GL032A100FAI013 | 64 Megabit, 32 Megabit, and 16 Megabit 3.0-Volt only Page Mode Flash Memory Featuring 200 nm MirrorBit Process Technology |

| S29GL032A100FAIR10 | 64 Megabit, 32 Megabit, and 16 Megabit 3.0-Volt only Page Mode Flash Memory Featuring 200 nm MirrorBit Process Technology |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| S25FL001D0FNFI003 | 制造商:SPANSION 制造商全稱:SPANSION 功能描述:2 Megabit, 1 Megabit CMOS 3.0 Volt Flash Memory with 25 MHz SPI Bus Interface |

| S25FL001D0FNFI011 | 制造商:SPANSION 制造商全稱:SPANSION 功能描述:2 Megabit, 1 Megabit CMOS 3.0 Volt Flash Memory with 25 MHz SPI Bus Interface |

| S25FL001D0FNFI013 | 制造商:SPANSION 制造商全稱:SPANSION 功能描述:2 Megabit, 1 Megabit CMOS 3.0 Volt Flash Memory with 25 MHz SPI Bus Interface |

| S25FL002D | 制造商:SPANSION 制造商全稱:SPANSION 功能描述:2 Megabit, 1 Megabit CMOS 3.0 Volt Flash Memory with 25 MHz SPI Bus Interface |

| S25FL002D0FMAI001 | 制造商:SPANSION 制造商全稱:SPANSION 功能描述:2 Megabit, 1 Megabit CMOS 3.0 Volt Flash Memory with 25 MHz SPI Bus Interface |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。