- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371106 > MH28D72KLG-10 (Mitsubishi Electric Corporation) 9,663,676,416-BIT (134,217,728-WORD BY 72-BIT) Double Data Rate Synchronous DRAM Module PDF資料下載

參數(shù)資料

| 型號: | MH28D72KLG-10 |

| 廠商: | Mitsubishi Electric Corporation |

| 英文描述: | 9,663,676,416-BIT (134,217,728-WORD BY 72-BIT) Double Data Rate Synchronous DRAM Module |

| 中文描述: | 9663676416位(134217728 - Word的72位),雙數(shù)據(jù)速率同步DRAM模塊 |

| 文件頁數(shù): | 22/39頁 |

| 文件大?。?/td> | 337K |

| 代理商: | MH28D72KLG-10 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁當(dāng)前第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁

MITSUBISHI LSIs

MITSUBISHI ELECTRIC

MH28D72KLG-75,-10

9,663,676,416-BIT (134,217,728-WORD BY 72-BIT) Double Data Rate Synchronous DRAM Module

MIT-DS-0412-0.1

21.Mar.2001

Preliminary Spec.

Some contents are subject to change without notice.

22

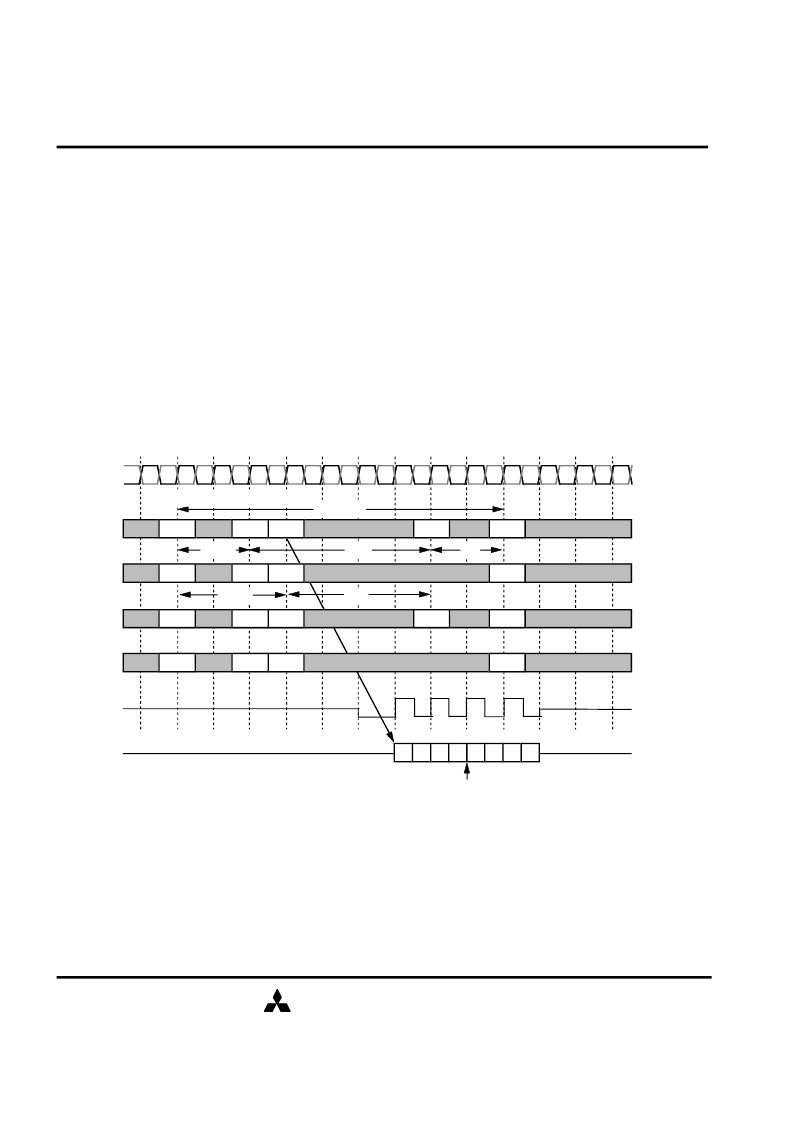

A precharge command can be issued at BL/2(Discrete) from a read command without data loss.

Precharge all

Bank Activation and Precharge All (BL=8, CL=2 (Discrete level))

Command

A0-9,11-12

A10

BA0,1

DQ

ACT

Xa

Xa

00

READ

Y

0

00

ACT

Xb

Xb

01

PRE

tRRD

tRCD

1

ACT

Xb

Xb

01

tRAS

tRP

tRCmin

2 ACT command / tRCmin

DQS

Qa0

BL/2

OPERATIONAL DESCRIPTION

BANK ACTIVATE

The DDR SDRAM has four independent banks. Each bank is activated by the ACT command

with the bank addresses (BA0,1). A row is indicated by the row address A12-0. The minimum

activation interval between one bank and the other bank is tRRD. Maximum 2 ACT commands

are allowed within tRC,although the number of banks which are active concurrently is not limited.

PRECHARGE

The PRE command deactivates the bank indicated by BA0,1. When multiple banks are active,

the precharge all command (PREA,PRE+A10=H) is available to deactivate them at the same

time. After tRP from the precharge, an ACT command to the same bank can be issued.

Qa1

Qa2 Qa3 Qa4 Qa5 Qa6 Qa7

/CLK

CLK

Module input and output timing.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MH28D72KLG-75 | 9,663,676,416-BIT (134,217,728-WORD BY 72-BIT) Double Data Rate Synchronous DRAM Module |

| MH28S72PJG-5 | Circular Connector; Body Material:Aluminum Alloy; Series:KPSE07; No. of Contacts:19; Connector Shell Size:14; Connecting Termination:Crimp; Circular Shell Style:Jam Nut Receptacle; Circular Contact Gender:Pin RoHS Compliant: No |

| MH28S72PJG-6 | Circular Connector; Body Material:Aluminum Alloy; Series:KPSE07; No. of Contacts:19; Connector Shell Size:14; Connecting Termination:Crimp; Circular Shell Style:Jam Nut Receptacle; Circular Contact Gender:Socket RoHS Compliant: No |

| MH28S72PJG-7 | KPSE 19C 19#20 SKT RECP |

| MH2M365CXJ-5 | HYPER PAGE MODE 75497472-BIT ( 2097152-WORD BY 36-BIT ) DYNAMIC RAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MH28D72KLG-75 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:9,663,676,416-BIT (134,217,728-WORD BY 72-BIT) Double Data Rate Synchronous DRAM Module |

| MH28FAD | 制造商:MTRONPTI 制造商全稱:MTRONPTI 功能描述:8 pin DIP, 3.3 or 5.0 Volt, HCMOS/TTL Clock Oscillator |

| MH28FAD-R | 制造商:MTRONPTI 制造商全稱:MTRONPTI 功能描述:8 pin DIP, 3.3 or 5.0 Volt, HCMOS/TTL Clock Oscillator |

| MH28FAD-R-1.96608MHZ | 制造商:MtronPTI 功能描述: |

| MH28FAD-R-32.000MHZ | 制造商:MtronPTI 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。