- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄384641 > M5M4V4405CTP-7S (Mitsubishi Electric Corporation) EDO (HYPER PAGE MODE) 4194304-BIT(1048576-WORD BY 4-BIT) DYNAMIC RAM PDF資料下載

參數(shù)資料

| 型號(hào): | M5M4V4405CTP-7S |

| 廠商: | Mitsubishi Electric Corporation |

| 英文描述: | EDO (HYPER PAGE MODE) 4194304-BIT(1048576-WORD BY 4-BIT) DYNAMIC RAM |

| 中文描述: | 江戶(超頁(yè)模式)4194304位(1048576 - Word的4位)動(dòng)態(tài)隨機(jī)存儲(chǔ)器 |

| 文件頁(yè)數(shù): | 3/27頁(yè) |

| 文件大?。?/td> | 293K |

| 代理商: | M5M4V4405CTP-7S |

第1頁(yè)第2頁(yè)當(dāng)前第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)

EDO (HYPER PAGE MODE) 4194304-BIT(1048576-WORD BY 4-BIT) DYNAMIC RAM

M5M4V4405CJ,TP-6,-7,-6S,-7S

MITSUBISHI LSIs

Average supply current

from V

CC

refreshing

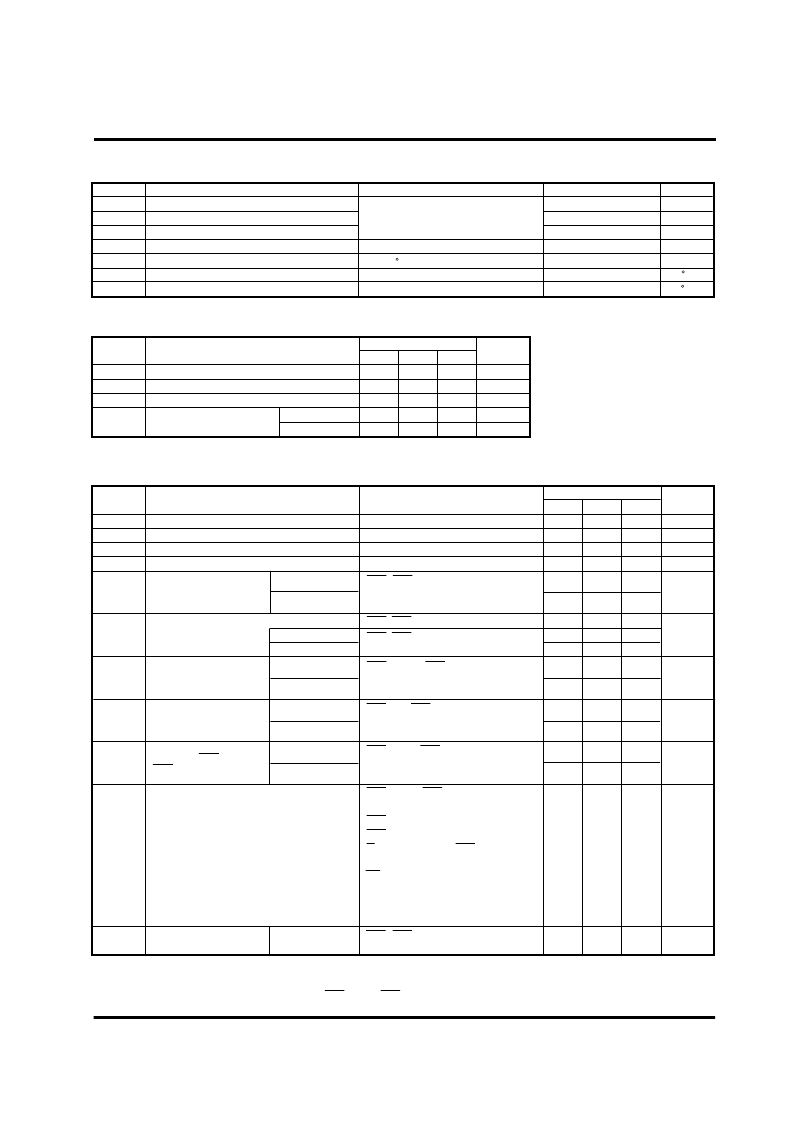

ABSOLUTE MAXIMUM RATINGS

Ratings

-0.5 ~ 4.6

-0.5 ~ 4.6

3

Symbol

V

CC

V

I

V

O

I

O

P

d

T

opr

T

stg

Parameter

Unit

V

V

V

mA

mW

C

C

-0.5 ~ 4.6

50

1000

0 ~ 70

-65 ~ 150

Ta=25

RECOMMENDED OPERATING CONDITIONS

(Ta=0~70C, unless otherwise noted)

(Note 1)

Unit

Limits

Nom

3.3

0

Min

3.0

0

2.0

-0.3

Max

3.6

0

V

V

V

V

V

0.8

Parameter

V

CC

V

SS

V

IH

Symbol

V

IL

V

CC

+0.3

0.8

-0.3

ELECTRICAL CHARACTERISTICS

(Ta=0~70C, V

CC

=3.3V± 0.3V, Vs

S=

0V, unless otherwise noted)

(Note 2)

V

OH

V

OL

I

OZ

I

I

High-level output voltage

Low-level output voltage

Off-state output current

Input current

Average supply current

from V

CC

operating

I

OH

=-2mA

I

OL

=2mA

Q floating, 0V

≤

V

OUT

≤

V

CC

0V

≤

V

IN

≤

V

CC

+0.3V, Other inputs pins=0V

V

V

μA

μA

Vcc

0.4

5

5

2.4

0

-5

-5

RAS=CAS

≥

V

CC

-0.2V

output open

70

Note 2: Current flowing into an IC is positive, out is negative.

3: I

CC1 (AV)

, I

CC3 (AV)

, I

CC4 (AV)

and I

CC6 (AV)

are dependent on cycle rate. Maximum current is measured at the fastest cycle rate.

4: I

CC1 (AV)

and I

CC4 (AV)

are dependent on output loading. Specified values are obtained with the output open.

5: Column Addres can be changed once or less while RAS=V

IL

and CAS=V

IH

.

C

Note 1 : All voltage values are with respect to V

SS.

Symbol

Parameter

Test conditions

Unit

Limits

Typ

Min

Max

DQ

1

~DQ

4

others

I

CC8(AV)*

I

CC9(AV)*

(Note 6)

Average supply current

from V

CC

Extended-Refresh cycle

Average supply current

from V

Self-Refresh cycle

(Note 6)

RAS cycling CAS

≤

0.2V or CAS

before RAS refresh cycling

RAS

≤

0.2V or

≥

V

CC

-0.2V

CAS

≤

0.2V or

≥

V

CC

-0.2V

W

≤

0.2V (Except for RAS falling

edge) or

≥

V

CC

-0.2V

OE

≤

0.2V or

≥

V

CC

-0.2V

A

0

~A

9

≤

0.2V or

≥

V

CC

-0.2V

DQ=open

t

RC

=125μs, t

RAS

=t

RAS

min

~1μs

RAS=CAS

≤

0.2V

output open

μA

100

μA

100

M5M4V4405C-6,-6S

M5M4V4405C-7,-7S

I

CC1 (AV)

I

CC2 (AV)

(Note 3,4,5)

Supply current from Vc

C ,

stand-by

RAS, CAS cycling

t

RC

=t

WC

=min.

output open

RAS=CAS =V

IH

, output open

mA

mA

80

2

0.5

0.05

*

(Note 6)

I

CC3 (AV)

I

CC4(AV)

I

CC6(AV)

(Note 3,5)

(Note 3,4,5)

(Note 3)

Average supply current

CC

from V

Average supply current

CC,

CAS before

from V

RAS cycling, CAS= V

IH

t

RC

=min.

output open

RAS=V

IL

, CAS cycling

t

PC

=min.

output open

CAS before RAS refresh cycling

t

RC

=min.

output open

mA

mA

mA

80

70

80

70

70

60

M5M4V4405C-6,-6S

M5M4V4405C-7,-7S

M5M4V4405C-6,-6S

M5M4V4405C-7,-7S

M5M4V4405C-6,-6S

M5M4V4405C-7,-7S

Conditions

Supply voltage

Supply voltage

High-level input voltage, all inputs

Low-level input voltage

Supply voltage

Input voltage

Output voltage

Output current

Power dissipation

Operating temperature

Storage temperature

With respect to V

SS

M5M4V4405C

M5M4V4405C(S)

M5M4V4405C(S)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M5M5256DRV-12VXL-I | 262144-BIT (32768-WORD BY 8-BIT) CMOS STATIC RAM |

| M5M5256DRV-12VLL | 262144-BIT (32768-WORD BY 8-BIT) CMOS STATIC RAM |

| M5M5256DRV-12VLL-I | 262144-BIT (32768-WORD BY 8-BIT) CMOS STATIC RAM |

| M5M5256DRV-12VXL | 262144-BIT (32768-WORD BY 8-BIT) CMOS STATIC RAM |

| M5M5256DRV-15VLL | 262144-BIT (32768-WORD BY 8-BIT) CMOS STATIC RAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M5M4V4S40CTP-12 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:4M (2-BANK x 131072-WORD x 16-BIT) Synchronous DRAM |

| M5M4V4S40CTP-15 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:4M (2-BANK x 131072-WORD x 16-BIT) Synchronous DRAM |

| M5M4V64S20ATP-10 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:64M (4-BANK x 4194304-WORD x 4-BIT) Synchronous DRAM |

| M5M4V64S20ATP-10L | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:64M (4-BANK x 4194304-WORD x 4-BIT) Synchronous DRAM |

| M5M4V64S20ATP-12 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:64M (4-BANK x 4194304-WORD x 4-BIT) Synchronous DRAM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。