- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄180205 > M393B1K73CH0-YH9 1G X 72 MULTI DEVICE DRAM MODULE, 0.255 ns, DMA240 PDF資料下載

參數(shù)資料

| 型號(hào): | M393B1K73CH0-YH9 |

| 元件分類: | DRAM |

| 英文描述: | 1G X 72 MULTI DEVICE DRAM MODULE, 0.255 ns, DMA240 |

| 封裝: | HALOGEN FREE AND ROHS COMPLIANT, DIMM-240 |

| 文件頁(yè)數(shù): | 14/53頁(yè) |

| 文件大小: | 1492K |

| 代理商: | M393B1K73CH0-YH9 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)當(dāng)前第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)

- 21 -

datasheet

DDR3L SDRAM

Rev. 1.01

Registered DIMM

1:2

R

E

G

I

S

T

E

R

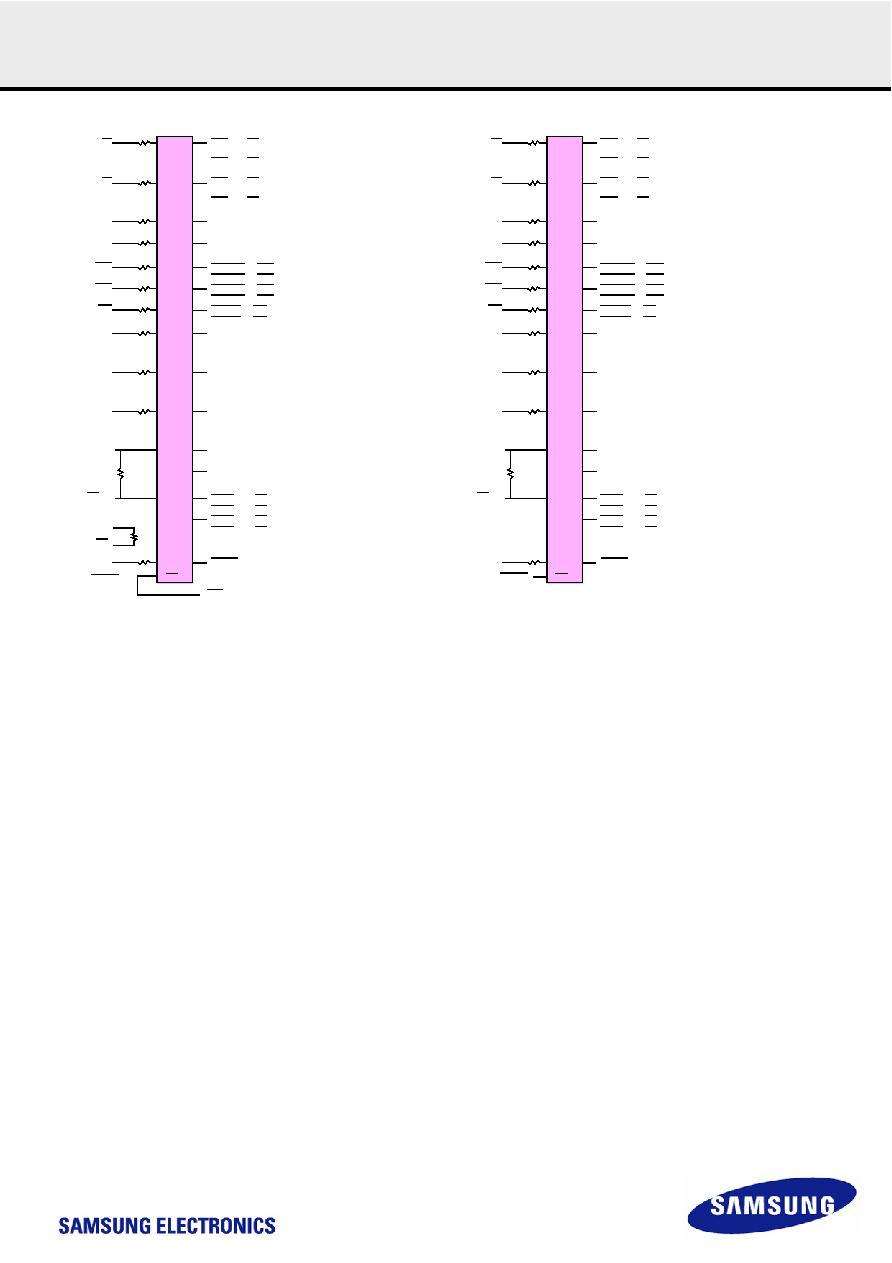

S1

BA[N:0]

A[N:0]

RAS

CAS

WE

CKE0

PST : SDRAMs D[71:0]

ARS1B-> CS0 : SDRAMs D10, D12, D14, D16

ARBA[N:0]A -> BA[N:0] : SDRAMs D[9:0], D[27:18]

ARA[N:0]A -> A[N:0] : SDRAMs D[9:0], D[27:18]

ARRASA -> RAS : SDRAMs D[9:0], D[27:18]

ARCASA -> CAS : SDRAMs D[9:0], D[27:18]

ARCKE0A -> CKE1 : SDRAMs D1, D3, D5, D7, D9

PAR_IN

S0

ARS0A-> CS1 : SDRAMs D1, D3, D5, D7, D9

ARBA[N:0]B -> BA[N:0] : SDRAMs D[17:10], D[35:28]

ARA[N:0]B -> A[N:0] : SDRAMs D[17:10], D[35:28]

ARRASB -> RAS : SDRAMs D[17:10], D[35:28]

ARCASB -> CAS : SDRAMs D[17:10], D[35:28]

ARWEA -> WE : SDRAMs D[9:0], D[27:18]

ARWEB -> WE : SDRAMs D[17:10], D[35:28]

ARCKE0B -> CKE1 : SDRAMs D11, D13, D15, D17

APCK1A -> CK : SDRAMs D[27:18]

APCK1B -> CK : SDRAMs D[35:28]

APCK0A -> CK : SDRAMs D[9:0]

APCK0B -> CK : SDRAMs D[17:10]

CKE1

ARCKE1A -> CKE0 : SDRAMs D0, D2, D4, D6, D8

ARCKE1B -> CKE0 : SDRAMs D10, D12, D14, D16

ODT0

ARODT0A -> ODT1 : SDRAMs D1, D3, D5, D7, D9

ARODT0B -> ODT1 : SDRAMs D11, D13, D15, D17

APCK0A -> CK : SDRAMs D[9:0]

APCK0B -> CK : SDRAMs D[17:10]

APCK1A -> CK : SDRAMs D[27:18]

APCK1B -> CK : SDRAMs D[35:28]

ARS0B-> CS1 : SDRAMs D11, D13, D15, D17

ARS1A-> CS0 : SDRAMs D0, D2, D4, D6, D8

CK0_c

CK0_t

120

Ω

CK1

120

Ω

Err_out

RST_n

RESET

D19, D21, D23, D25, D27

D29, D31, D33, D35

D18, D20, D22, D24, D26

D28, D30, D32, D34

D19, D21, D23, D25, D27

D29, D31, D33, D35

D18, D20, D22, D24, D26

D28, D30, D32, D34

D19, D21, D23, D25

D29, D31, D33, D35

1:2

R

E

G

I

S

T

E

R

S3

BA[N:0]

A[N:0]

RAS

CAS

WE

CKE0

BRS3B-> CS0 : SDRAMs D36, D38, D40, D42

BRBA[N:0]A -> BA[N:0] : SDRAMs D[53:44], D[71:62]

BRA[N:0]A -> A[N:0] : SDRAMs D[53:44], D[71:62]

BRRASA -> RAS : SDRAMs D[53:44], D[71:62]

BRCASA -> CAS : SDRAMs D[53:44], D[71:62]

BRCKE0A -> CKE1 : SDRAMs D45, D47, D49, D51, D53

PAR_IN

S2

BRS2A-> CS1 : SDRAMs D45, D47, D49, D51, D53

BRBA[N:0]B -> BA[N:0] : SDRAMs D[43:36], D[61:54]

BRA[N:0]B -> A[N:0] : SDRAMs D[43:36], D[61:54]

BRRASB -> RAS : SDRAMs D[43:36], D[61:54]

BRCASB -> CAS : SDRAMs D[43:36], D[61:54]

BRWEA -> WE : SDRAMs D[53:44], D[71:62]

BRWEB -> WE : SDRAMs D[43:36], D[61:54]

BRCKE0B -> CKE1 : SDRAMs D37, D39, D41, D43

BPCK1A -> CK : SDRAMs D[71:62]

BPCK1B -> CK : SDRAMs D[61:54]

BPCK0A -> CK : SDRAMs D[53:44]

BPCK0B -> CK : SDRAMs D[43:36]

CKE1

BRCKE1A -> CKE0 : SDRAMs D44, D46, D48, D50, D52

BRCKE1B -> CKE0 : SDRAMs D36, D38, D40, D42

ODT1

BRODT1A -> ODT1 : SDRAMs D45, D47, D49, D51, D53

BRODT1B -> ODT1 : SDRAMs D37, D39, D41, D43

BPCK0A -> CK : SDRAMs D[53:44]

BPCK0B -> CK : SDRAMs D[43:36]

BPCK1A -> CK : SDRAMs D[71:62]

BPCK1B -> CK : SDRAMs D[61:54]

BRS2B-> CS1 : SDRAMs D37, D39, D41, D43

BRS3A-> CS0 : SDRAMs D44, D46, D48, D50, D52

CK0_c

CK0_t

120

Ω

Err_out

RST_n

RESET

D63, D65, D67, D69, D71

D55, D57, D59, D61

D62, D64, D66, D68, D70

D54, D56, D58, D60

D63, D65, D67, D69, D71

D55, D57, D59, D61

D62, D64, D66, D68, D70

D54, D56, D58, D60

D63, D65, D67, D69, D71

D55, D57, D59, D61

A

B

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M393B5273CH0-CK0 | 512M X 72 MULTI DEVICE DRAM MODULE, 0.225 ns, DMA240 |

| M393B5773CH0-CK0 | 256M X 72 MULTI DEVICE DRAM MODULE, 0.225 ns, DMA240 |

| M3950/1529A012 | TOGGLE SWITCH, 3PDT, LATCHED, 4A, 28VDC, THROUGH HOLE-STRAIGHT |

| M83731/2327D110 | TOGGLE SWITCH, 3PDT, MOMENTARY, 4A, 28VDC, THROUGH HOLE-STRAIGHT |

| M3950/1726A110 | TOGGLE SWITCH, 3PDT, LATCHED, 4A, 28VDC, THROUGH HOLE-STRAIGHT |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M393B1K73EB0 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:240pin Registered DIMM based on 2Gb E-die |

| M393B273DH0-CH9E8 | 制造商:Samsung Semiconductor 功能描述:4GB 2RX8 PC3-8500R-07-00-B0-D1 - Trays |

| M393B2873EH1 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:DDR3 SDRAM Memory |

| M393B2873EH1-CF8 | 制造商:ATP Electronics Inc 功能描述:M393B2873EH1-CF8 - Bulk |

| M393B2873FH0 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:DDR3 SDRAM Memory |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。