- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄358865 > LM4560 (National Semiconductor Corporation) Advanced PCI Audio Accelerator PDF資料下載

參數(shù)資料

| 型號(hào): | LM4560 |

| 廠商: | National Semiconductor Corporation |

| 英文描述: | Advanced PCI Audio Accelerator |

| 中文描述: | 先進(jìn)的PCI音頻加速器 |

| 文件頁(yè)數(shù): | 33/54頁(yè) |

| 文件大?。?/td> | 380K |

| 代理商: | LM4560 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)當(dāng)前第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)

4.0 Functional Description

(Continued)

Channels which don’t require PCI bus cycle, i.e. cache hit

channels and I2StoMIX channel, have lower priority.

Channels which depend on other channel’s result, i.e.

Main Mixer Capture channel, Chorus Send channel and

Reverb Send channel, have the lowest priority.

Basically, all operation of one channel include address generation, data reading/writing, interpolation, per channel LFO, low fre-

quency FM/AM, Envelope calculation, PAN, volume adjusting and mixer accumulation. We call it Channel Operation. After all

channel’s operation are done, the mixing result will be sent to FIFO. We call this Mixing Loop.

Before each Mixing Loop, Scheduler scans cache hit/miss flags of all active channels to decide the processing sequence of the

current Loop.

4.1.2 Address Engine

Address generation, data reading/writing, per channel LFO, low frequency FM and interpolation coefficient calculation are pro-

cessed by Address Engine.

Terms:

CCI (6 bits)— Current Channel Index

CPTR (1 bit)— Cache Pointer

ESO (16 bits)— Ending Sample Offset (relative to loop begin sample)

CSO (16 bits)— Current Sample Offset (relative to loop begin sample)

CSO_SIGN (1 bit)— Sign bit of CSO

CAO (18 bits) — Current Address Offset (relative to loop begin address)

LBA (32 bits)— Loop Begin Address

CSA (32 bits)— Current Sample Address

FMS (4 bits)— Frequency Modulation Step

FMC (2 bit)— Frequency Modulation Control

SIN (4 bits)— current state of sin counter

FMA (8 bits)— Frequency Modulation Amount

BL (2 bits)— Burst read Length

DELTA (15 bits)— Sample increment number per 48 kHz clock (format 3.12)

ALPHA (12 bits)— Interpolation coefficient, i.e. fractional part of CSO

NEWCSO (16 bits)— the next CSO

NEWALPHA (12 bits)— the next ALPHA

The procedure of address engine is described as following:

(1) Load RegE0h // read FMS, CSO, ALPHA from ARAM

Load RegE4h // read LBA from ARAM

if (8 bit && MONO) CAO = CSO;

else if (16 bit && STEREO) CAO = CSO

<<

2;

else CAO = CSO

<<

1;

FMA = SIN*FMS;

(3) Load RegE8h // read ESO, DELTA, CPTR from ARAM

if(Cache miss)

{ // calculate address CSA = LBA + (CSO_SIGN==0) CAO : CAO; // 32 bit addition }

BL is decided by CSA[1:0] and data_type[2:1];

(data_type[2:0] refers to bit[15:13] of channel register F0h)

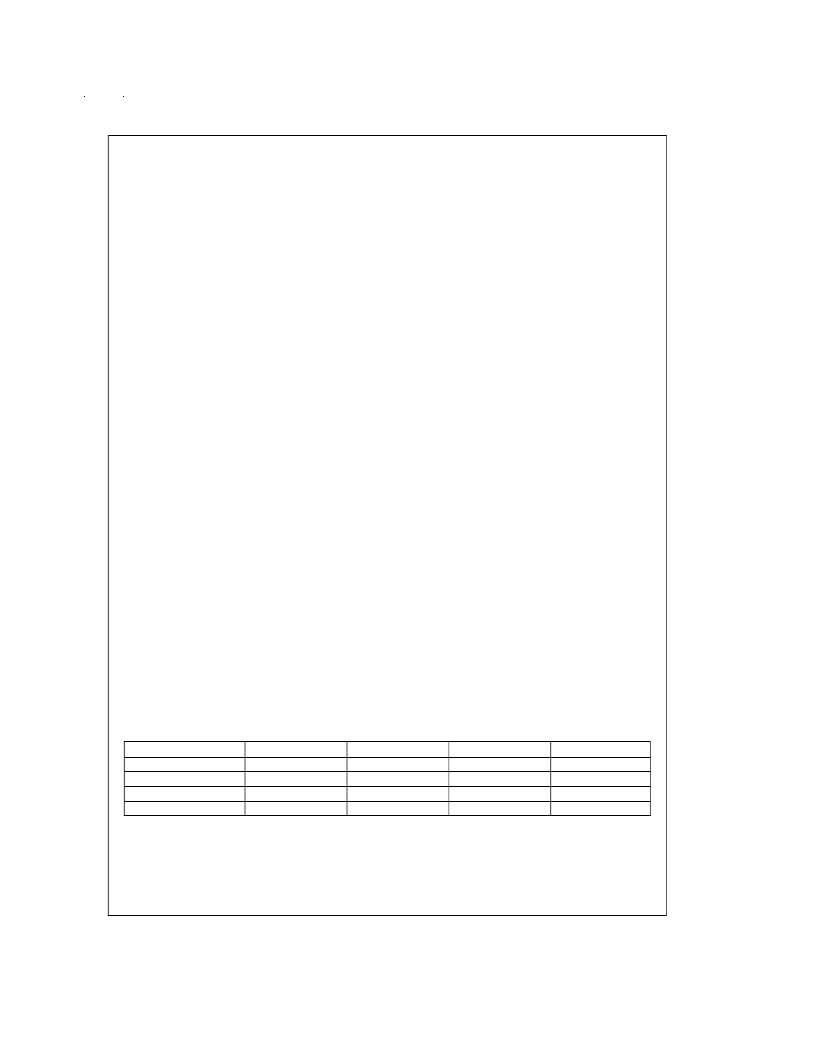

BL

CSA[1:0]=00

1

1

1

2

CSA[1:0]=01

1

2

2

3

CSA[1:0]=10

1

2

2

3

CSA[1:0]=11

2

2

2

3

Data_type[2:1]=00

Data_type[2:1]=01

Data_type[2:1]=10

Data_type[2:1]=11

BL (Burst Length)

Update RegE8h with new CPTR

Update RegECh with new LFO_CTRL & LFO_CT

www.national.com

33

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LM45BIM3 | SOT-23 Precision Centigrade Temperature Sensors |

| LM45BIM3X | SOT-23 Precision Centigrade Temperature Sensors |

| LM45B | SOT-23 Precision Centigrade Temperature Sensors |

| LM4610 | Dual DC Operated Tone/Volume/Balance Circuit with National 3-D Sound |

| LM4610N | Dual DC Operated Tone/Volume/Balance Circuit with National 3-D Sound |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LM4560VJD | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| LM4562 | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:Dual High Performance, High Fidelity Audio Operational Amplifier |

| LM4562_07 | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:Dual High Performance, High Fidelity Audio Operational Amplifier |

| LM4562HA | 制造商:Texas Instruments 功能描述:OP Amp Dual GP ??17V 8-Pin TO-99 Tray |

| LM4562HA/NOPB | 功能描述:運(yùn)算放大器 - 運(yùn)放 RoHS:否 制造商:STMicroelectronics 通道數(shù)量:4 共模抑制比(最小值):63 dB 輸入補(bǔ)償電壓:1 mV 輸入偏流(最大值):10 pA 工作電源電壓:2.7 V to 5.5 V 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-16 轉(zhuǎn)換速度:0.89 V/us 關(guān)閉:No 輸出電流:55 mA 最大工作溫度:+ 125 C 封裝:Reel |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。